# CALIBRATION and SERVICING HANDBOOK

Volume 1

1281

selfcal digital multimeter

# CALIBRATION and SERVICING HANDBOOK

for

# **THE DATRON 1281**

# SELFCAL **DIGITAL MULTIMETER**

Volume 1

# Calibration and Servicing Information

# **Technical Descriptions**

For any assistance contact your nearest Datron Sales and Service center. Addresses can be found at the back of this handbook.

850091

Issue 1 (JULY 1989)

# when connected to a high voltage source

FRONT or REAR terminals carry the Full Input Voltage

Guard terminal is sensitive to over-voltage

Unless are that it is to do so,

the or and

# **Volume 1 Contents**

Servicing Diagrams and Component Lists.

General Description, Installation, Controls, Operation, Applications; Specification, Specification Verification and Routine Calibration.

Refer to Volume 2

Refer to User's Handbook

| Secti | ion  | Title   |                                                      | Page |

|-------|------|---------|------------------------------------------------------|------|

| 1     | CAL  | BRAT    | ION                                                  |      |

|       | 1.1  | Routin  | e Calibration References                             | 1-1  |

|       | 1.2  |         | al Access                                            |      |

|       |      |         |                                                      |      |

|       | 1.3  | Remot   | te Calibration via the IEEE 488 Interface            | 1-1  |

|       | 1.4  | Specia  | Il Calibration                                       | 1-1  |

|       |      | 1.4.1   | Entry into the SPCL Menu                             | 1-2  |

|       |      | 1.4.2   | Adc Key                                              | 1-3  |

|       |      | 1.4.3   | Dac Key                                              | 1-4  |

|       |      | 1.4.4   | Freq                                                 | 1-5  |

|       |      | 1.4.5   | ClrNv                                                | 1-6  |

| 2     | GUID |         | 1281 FAULT DIAGNOSIS                                 |      |

|       | 2.1  | Introdu | uction                                               |      |

|       |      | 2.1.1   | Use of Error Codes                                   | 2-1  |

|       |      | 2.1.2   | Code Groupings                                       | 2-1  |

|       |      | 2.1.3   | 'Full' and 'Fast' Selftest                           | 2-2  |

|       |      | 2.1.4   | References                                           | 2-2  |

|       | 2.2  | 9000 S  | eries Codes - Fatal System Errors                    | 2-2  |

|       | 2.2  | 2.1.1   | Introduction                                         |      |

|       |      | 2.2.2   | Immediate Action                                     |      |

|       |      | 2.2.3   | Fatal System Error Codes                             |      |

|       | 2.3  |         | and Errors                                           |      |

|       | 0.4  |         |                                                      |      |

|       | 2.4  | 2.4.1   | eries Codes - Execution Errors                       |      |

|       |      | 2.4.1   | Execution Error Codes                                |      |

|       |      |         |                                                      |      |

|       | 2.5  |         | eries Codes - Device-Dependent Errors                |      |

|       |      | 2.5.1   | Introduction                                         |      |

|       |      | 2.5.2   | Index of Device-Dependent Error Codes                | 2-5  |

|       | 2.6  | 2000 S  | eries Codes - Device-Dependent Errors - Localization | 2-12 |

|       |      | 2.6.1   | Introduction                                         | 2-12 |

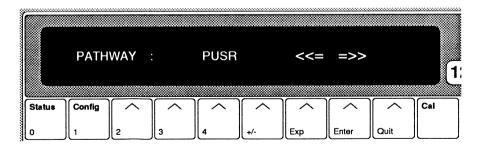

|       |      | 2.6.2   | Access to Error Codes via the 1281 Menu Keys         | 2-13 |

|       |      | 2.6.3   | Composition of the Error Code                        | 2-14 |

|       |      | 2.6.4   | External Calibration Operations                      |      |

|       |      | 2.6.5   | Memory Tests                                         | 2-15 |

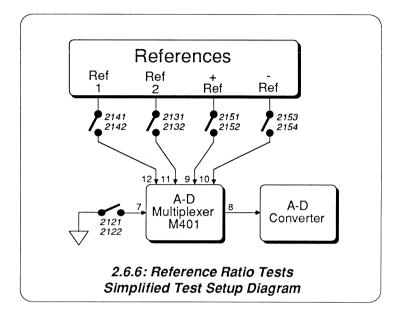

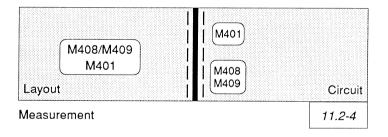

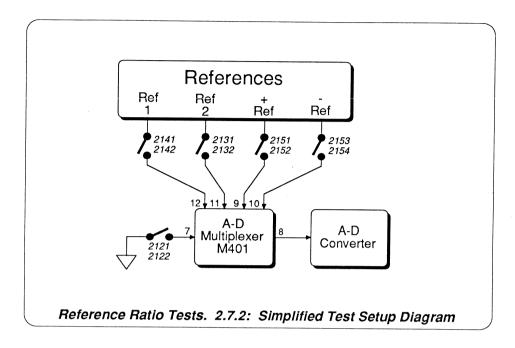

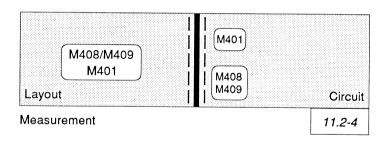

|       |      | 2.6.6   | Reference Ratio Tests                                |      |

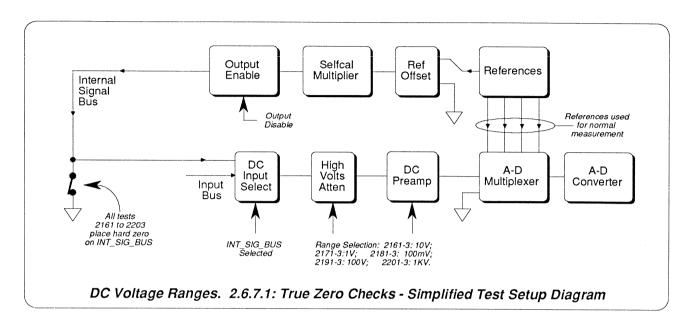

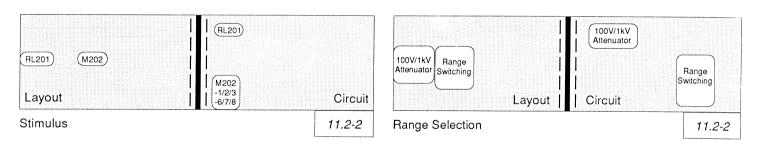

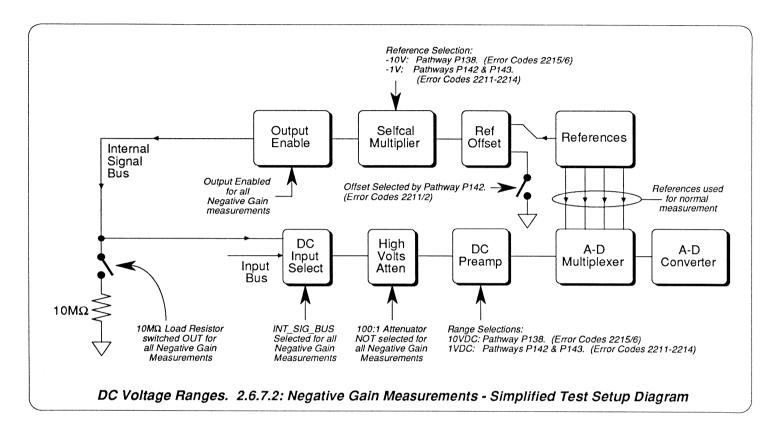

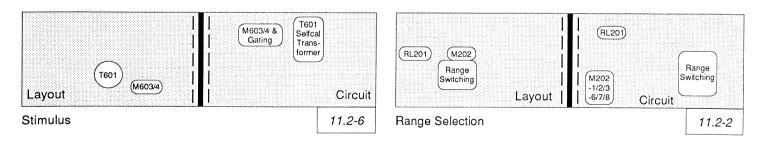

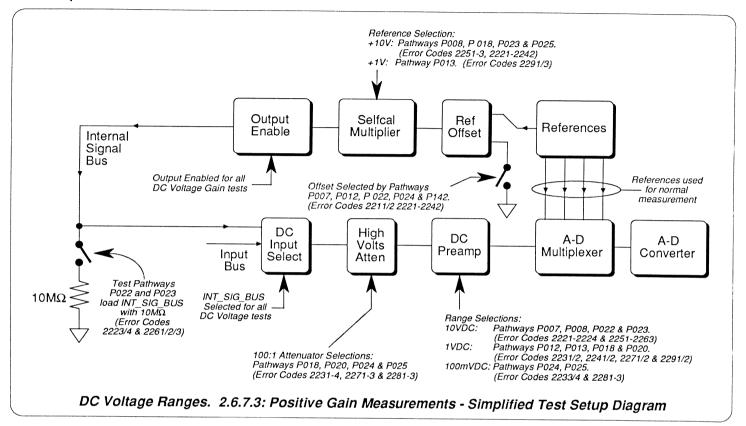

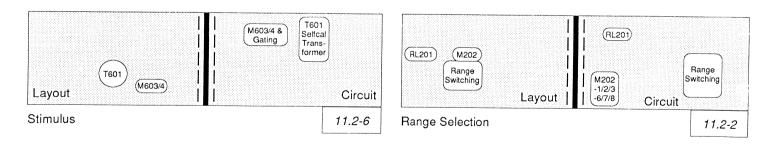

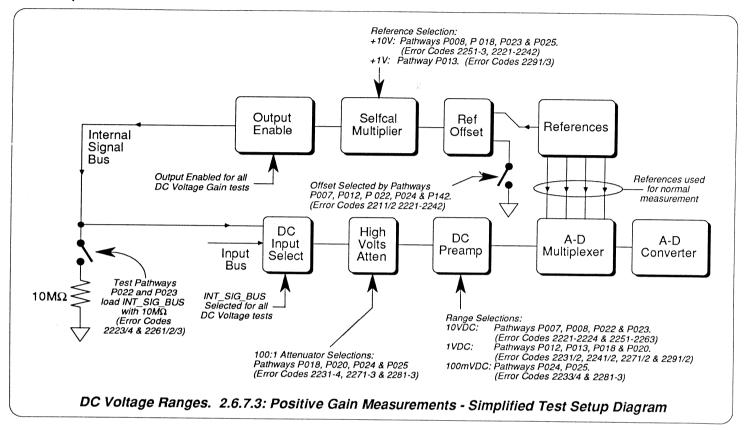

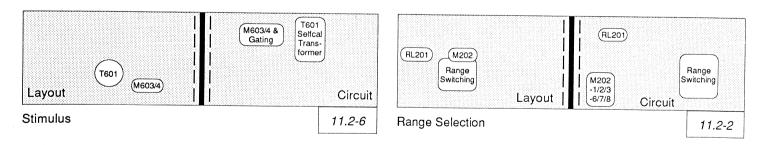

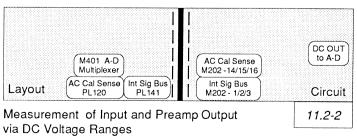

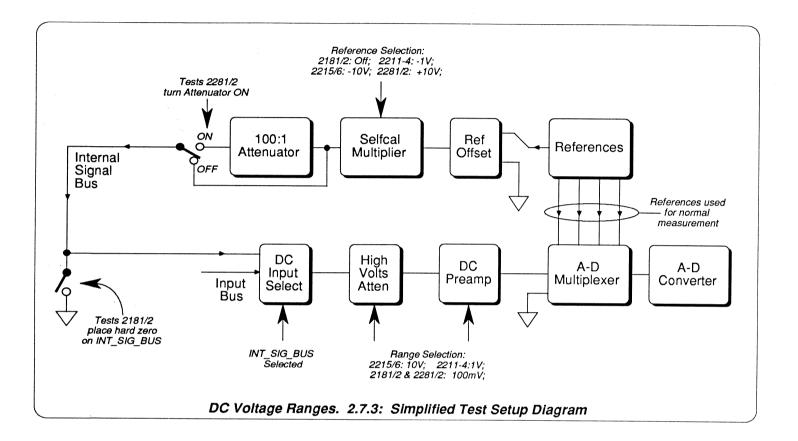

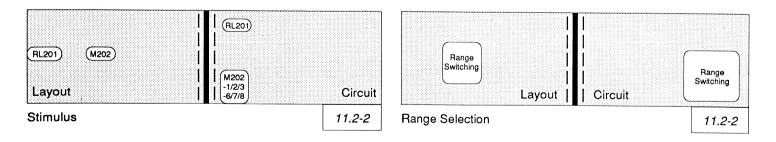

|       |      | 2.6.7   | DC Voltage Tests                                     |      |

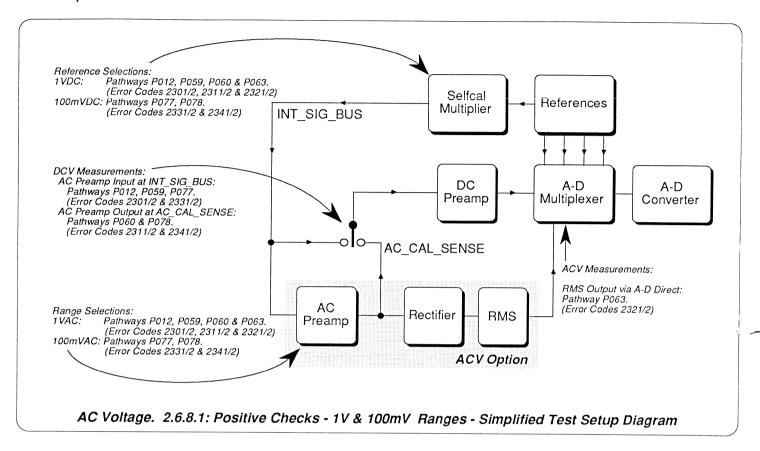

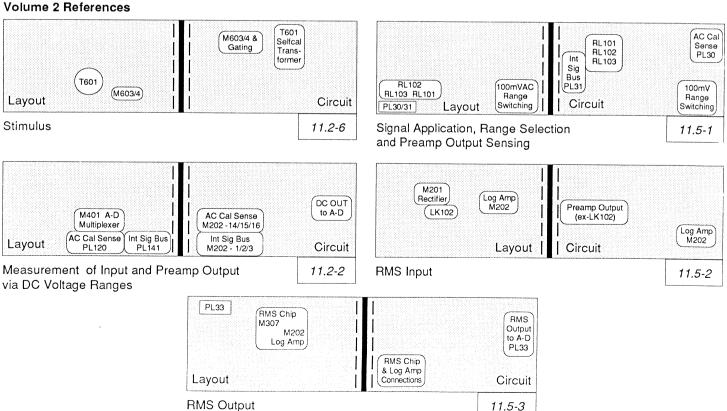

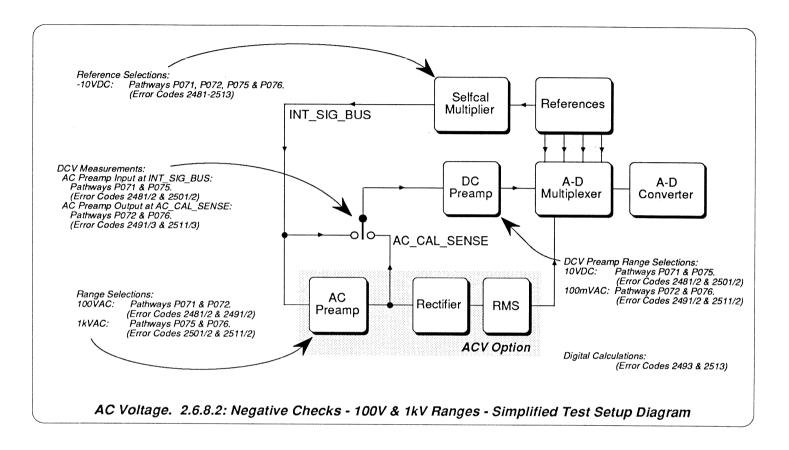

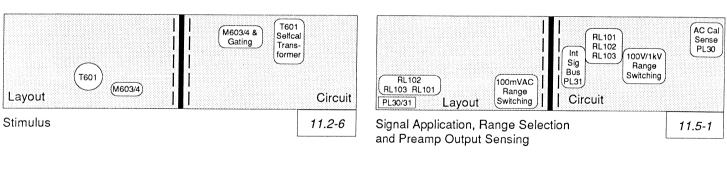

|       |      | 2.6.8   | AC Voltage Tests                                     |      |

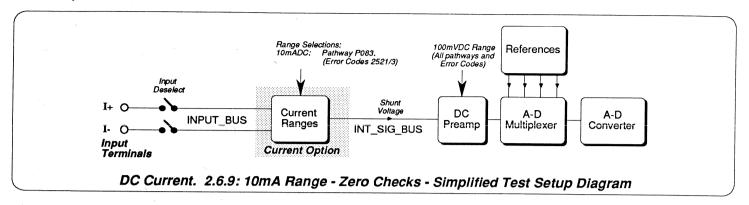

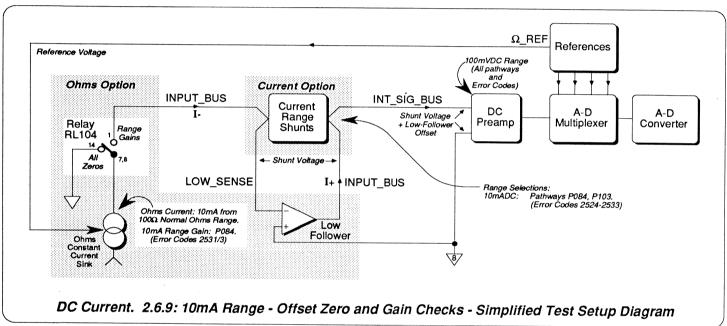

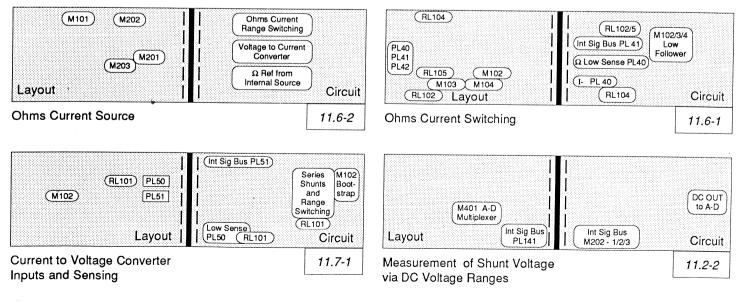

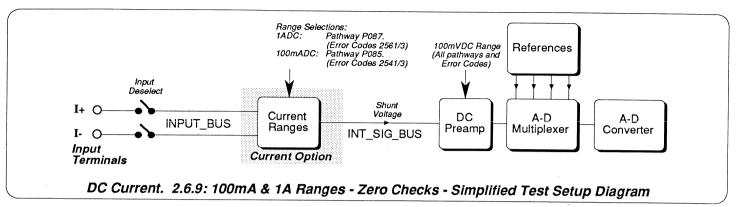

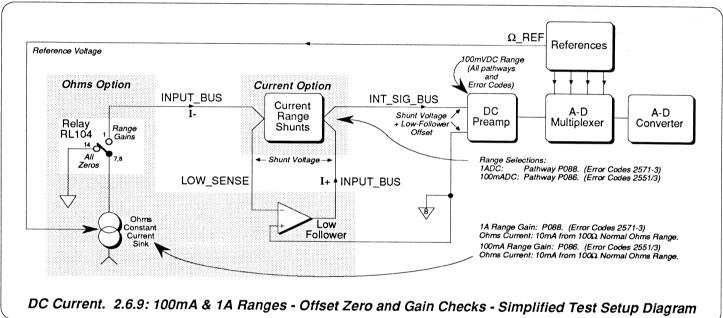

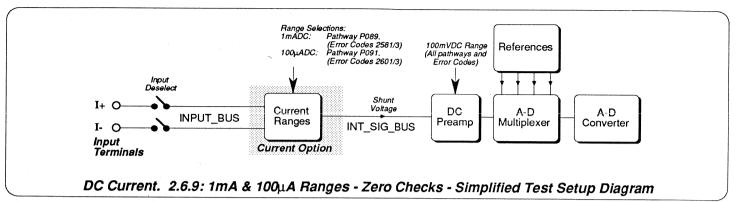

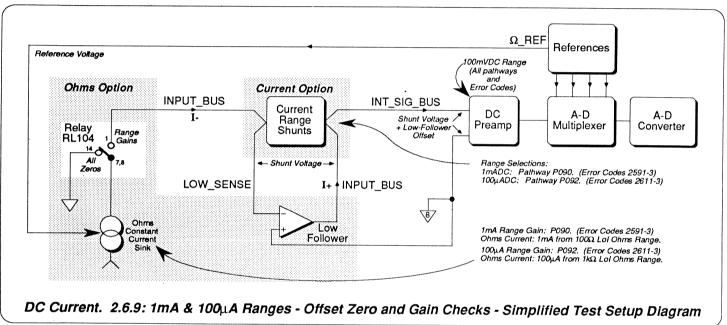

|       |      | 2.6.9   | DC Current Tests                                     |      |

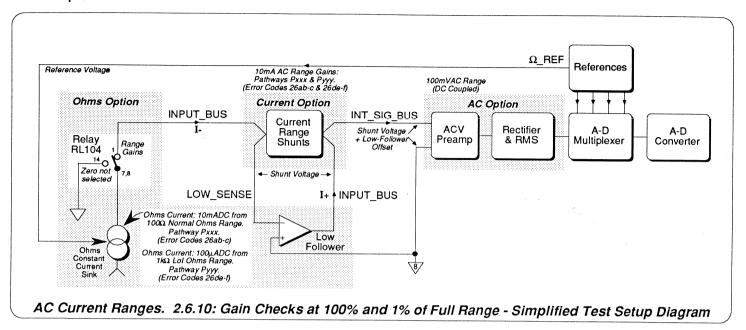

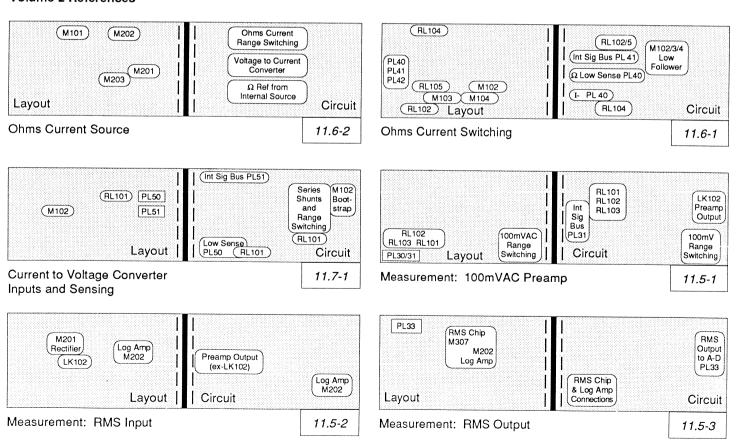

|       |      | 2.6.10  | AC Current Tests                                     | 2-42 |

|       |      |         | Resistor Ratio Tests                                 |      |

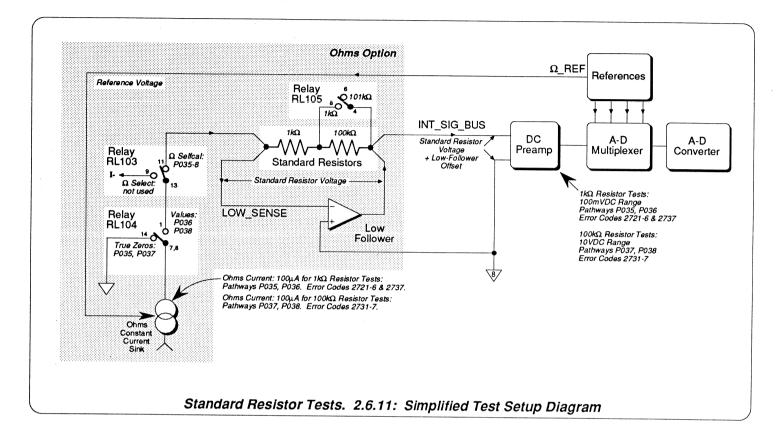

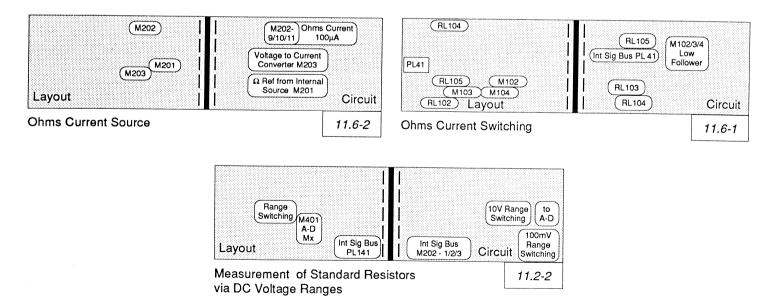

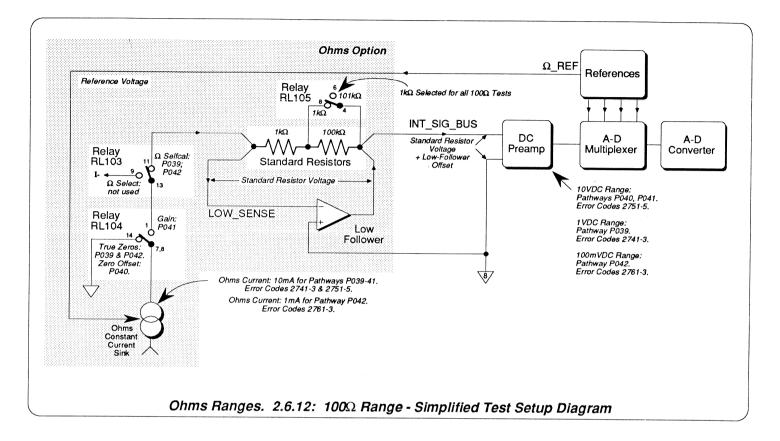

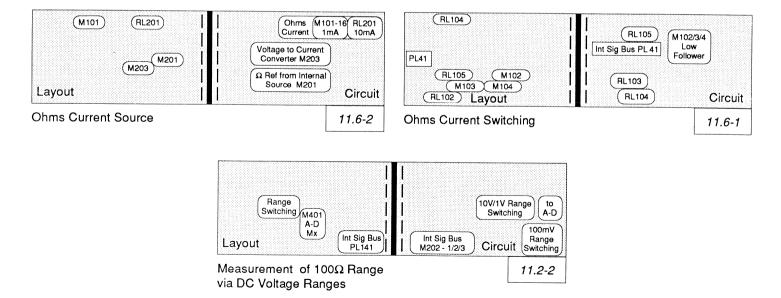

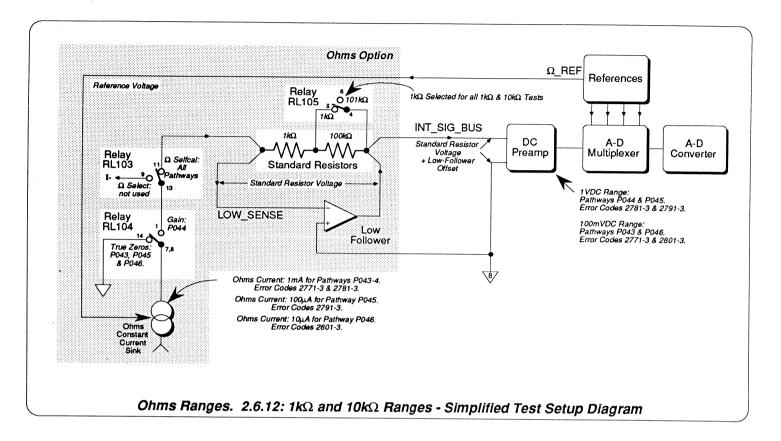

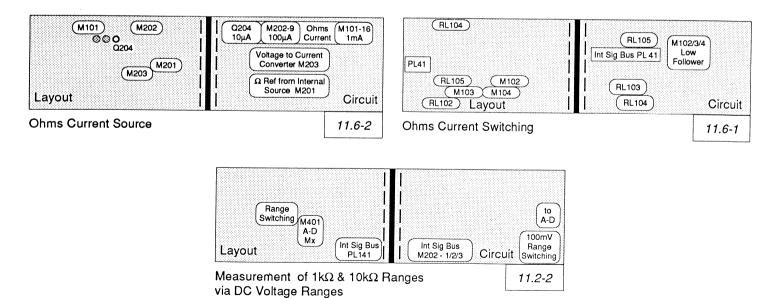

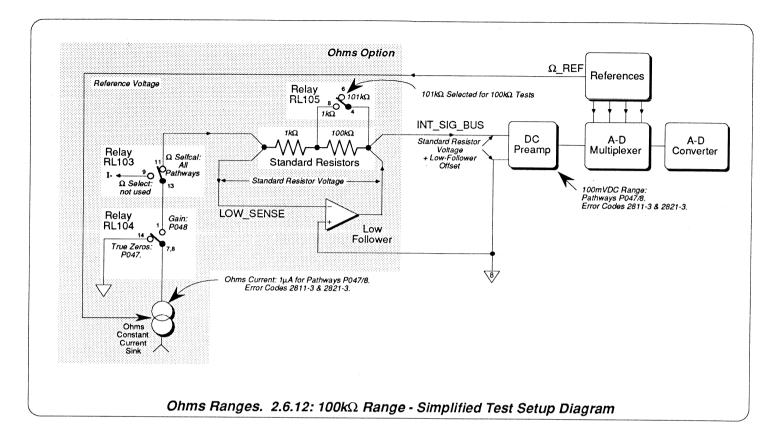

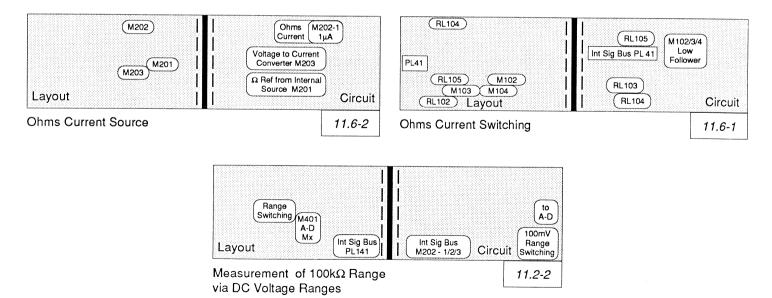

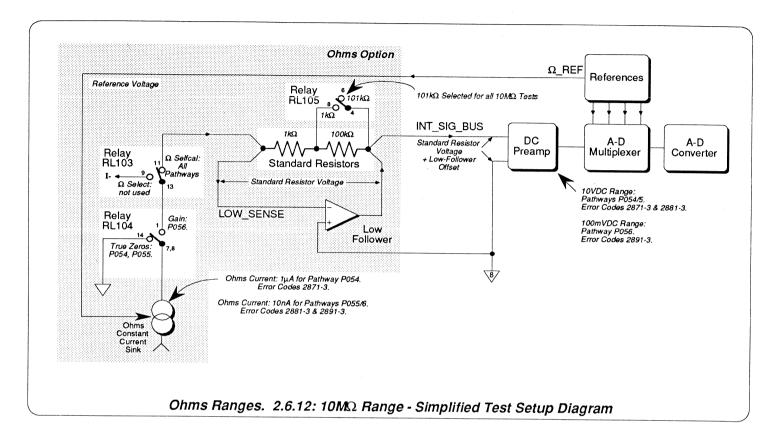

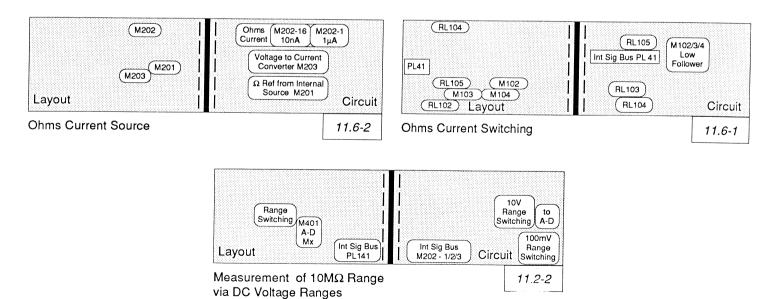

|       | 3 23 | 2.6.12  | Ohms Tests                                           | 2-50 |

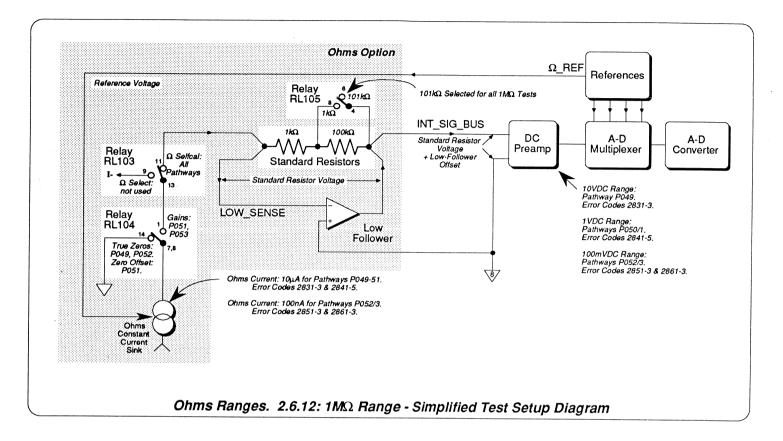

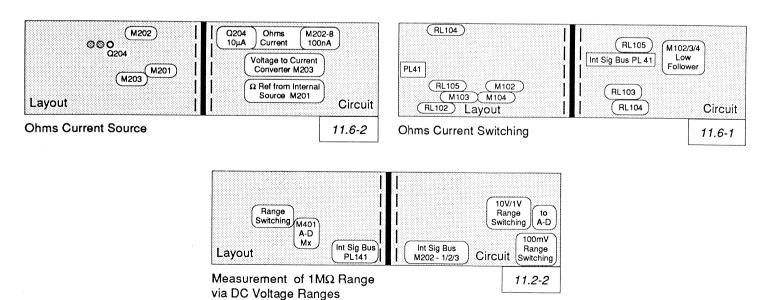

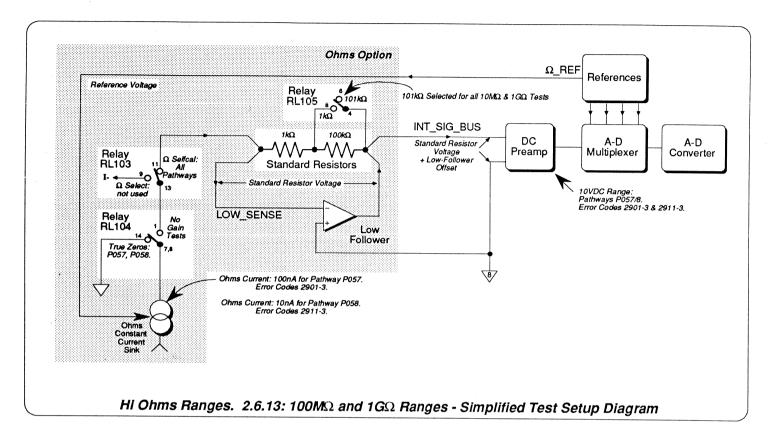

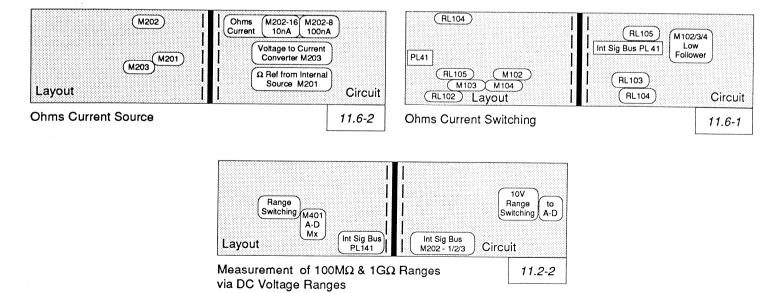

|       |      | 2.6.13  | High Ohms Tests                                      | 2-56 |

|       | 2.7  | Fast Se | elftest                                              | 2-58 |

|       |      | 2.7.1   | Memory Tests                                         |      |

|       |      | 2.7.2   | Reference Ratio Tests                                |      |

|       |      | 2.7.3   | DC Voltage Tests                                     |      |

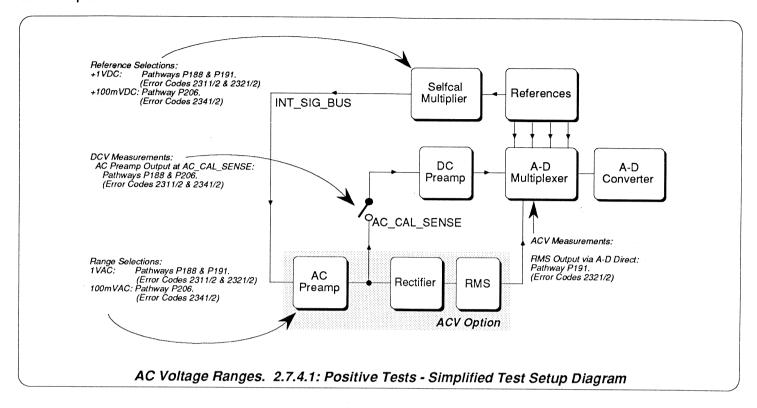

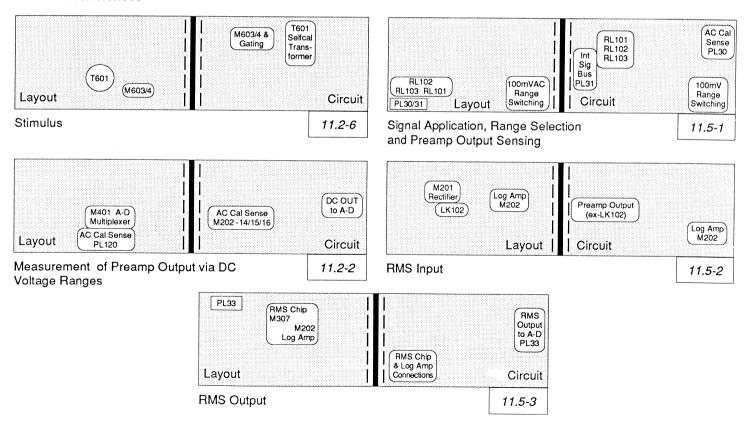

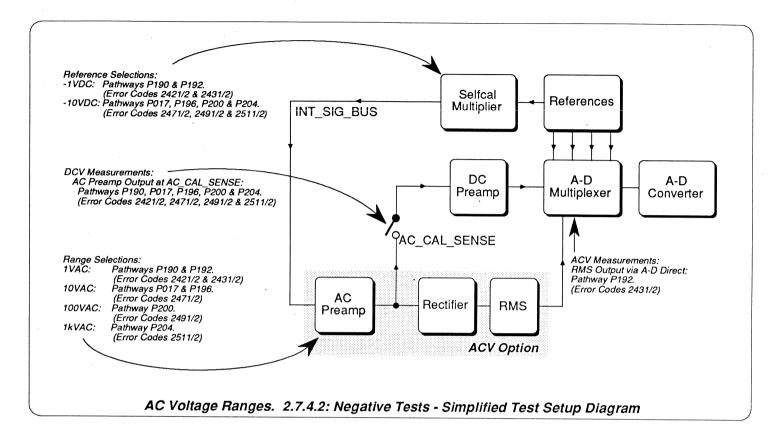

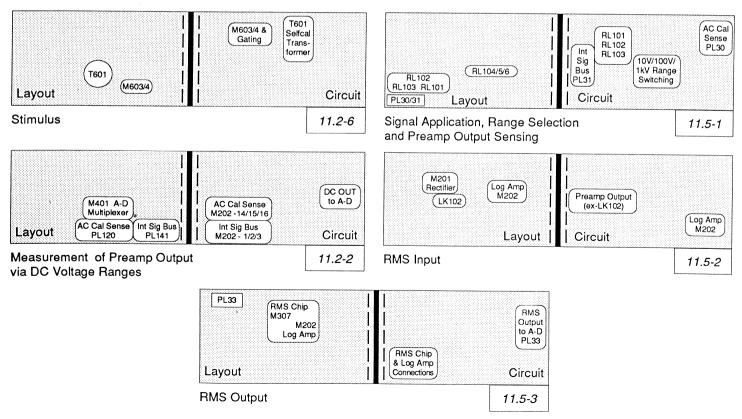

|       |      | 2.7.4   | AC Voltage Tests                                     |      |

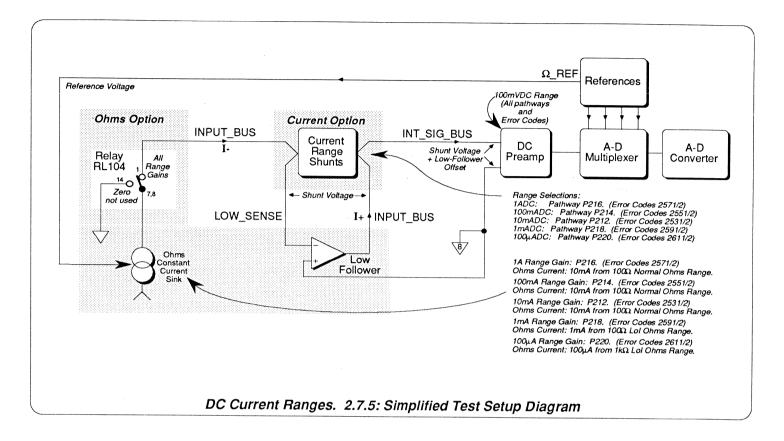

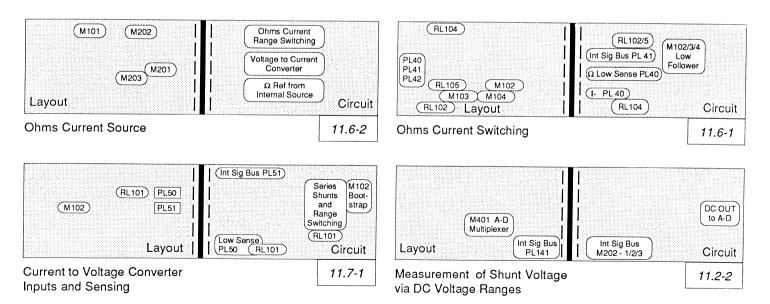

|       |      | 2.7.5   | DC Current Tests                                     |      |

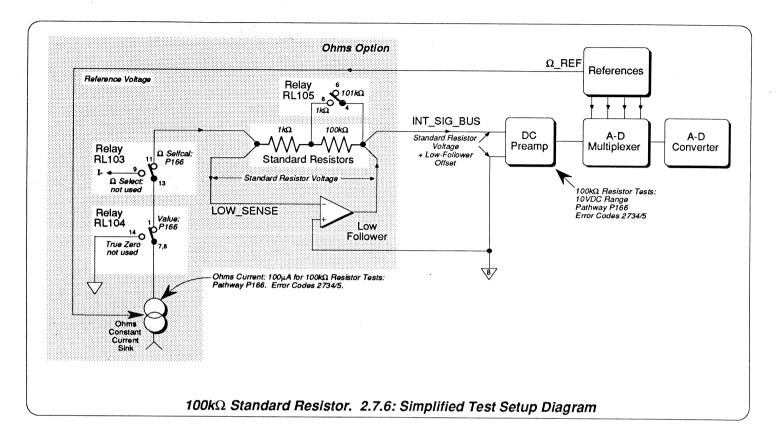

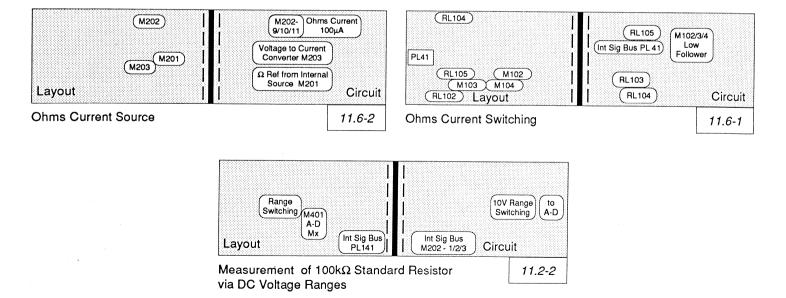

|       |      | 2.7.6   | Resistor Ratio Tests                                 | 2-68 |

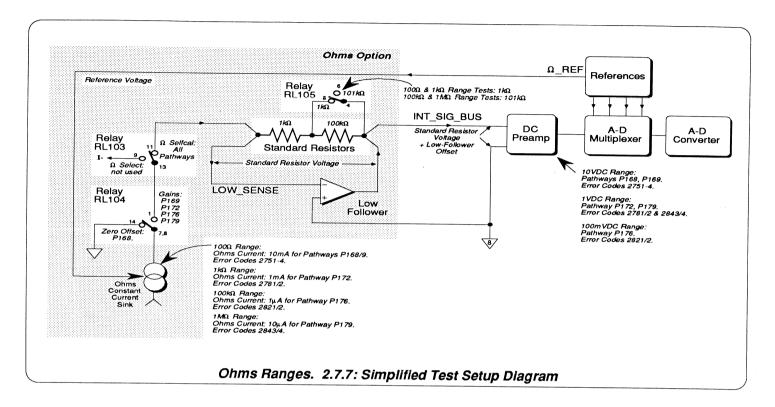

|       |      | 2.7.7   | Ohms Tests                                           |      |

|       |      |         |                                                      |      |

| Secti | on  | Title                                                                                                                                                                                               | Page                                                 |

|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 3     | DIS | MANTLING AND REASSEMBLY                                                                                                                                                                             |                                                      |

|       | 3.1 | General Precautions 3.1.1 WARNING 3.1.2 CAUTIONS                                                                                                                                                    | 3-1<br>3-1                                           |

|       | 3.2 | General Mechanical Layout                                                                                                                                                                           | 3-1                                                  |

|       | 3.3 | 3.3.1 External Construction                                                                                                                                                                         | 3-2<br>3-2                                           |

|       | 3.4 | General Access  3.4.1 Rear Corner Blocks, Top Cover  3.4.2 Rear Corner Blocks, Bottom Cover  3.4.3 Front Bezel  3.4.4 Rear Panel Assembly                                                           | 3-3<br>3-3<br>3-4                                    |

|       | 3.5 | Sub-Assembly Removal and Fitting  3.5.1 Digital PCB  3.5.2 Display PCB  3.5.3 Front Panel Switch PCB  3.5.4 Front Terminal Assembly  3.5.5 DC PCB  3.5.6 AC PCB.  3.5.7 Ohms PCB  3.5.8 Current PCB | 3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-8<br>3-9 |

|       | 3.6 | Front Terminal Retraction Mechanism                                                                                                                                                                 | 3-9                                                  |

|       | 3.7 | Transformer Assemblies                                                                                                                                                                              | 3-10                                                 |

| 4     | SEF | RVICING                                                                                                                                                                                             |                                                      |

|       | 4.1 | Routine Servicing                                                                                                                                                                                   | 4-1                                                  |

|       | 4.2 | Adjustment Following Replacement of PCBs                                                                                                                                                            | 4-1                                                  |

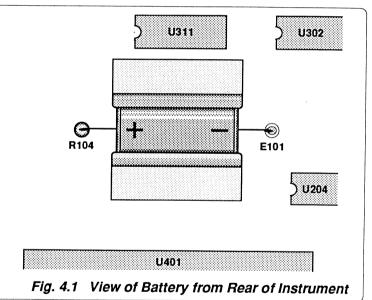

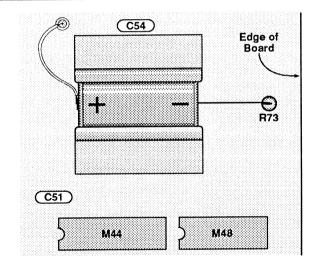

|       | 4.3 | Lithium Battery - Replacement                                                                                                                                                                       | 4-2                                                  |

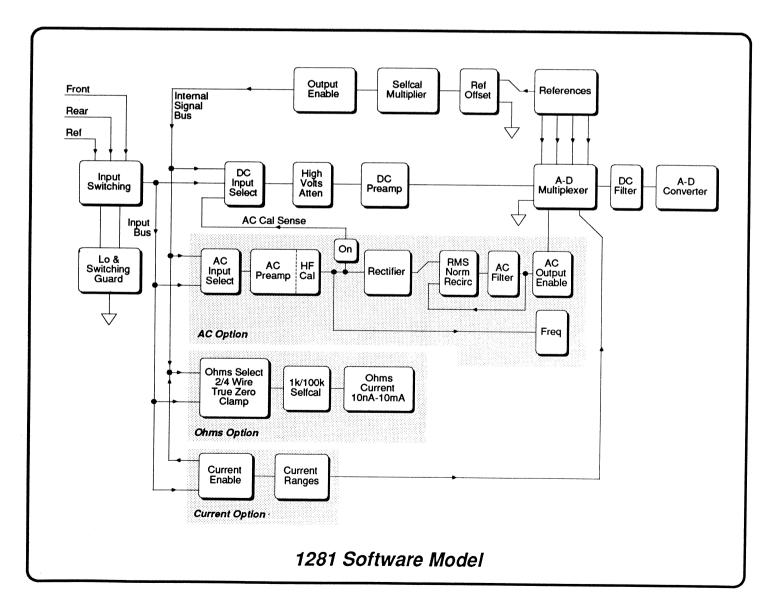

| 5     | TEC | CHNICAL DESCRIPTIONS                                                                                                                                                                                |                                                      |

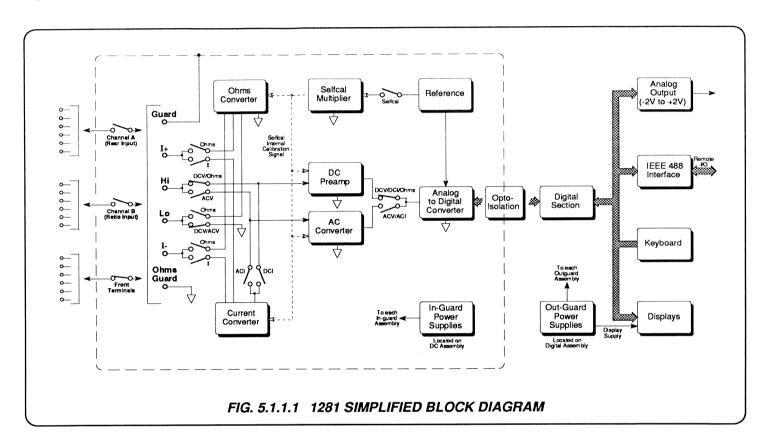

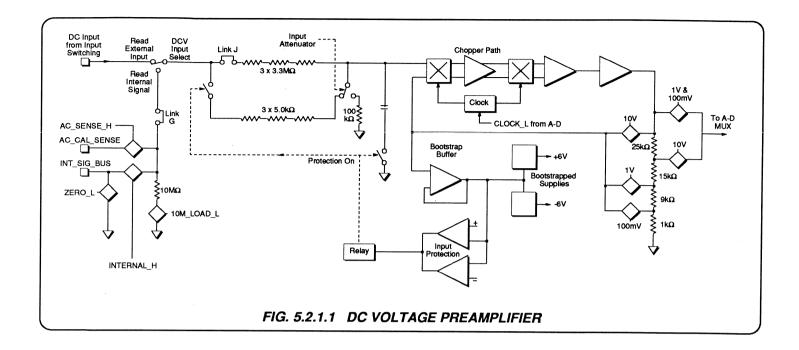

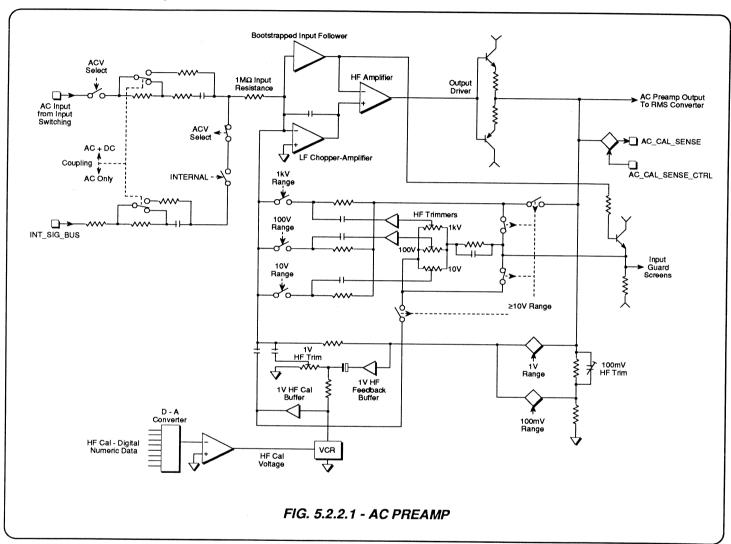

|       | 5.1 | Principles of Operation                                                                                                                                                                             | 5-3                                                  |

|       | 5.2 | PCB Descriptions                                                                                                                                                                                    | 5-7<br>5-12<br>5-18<br>5-23<br>5-26<br>5-36          |

# SECTION 1 CALIBRATION

## 1.1 Routine Calibration

The main features of the routine calibration facilities are described in the User's Handbook, covering:

External Calibration Section 8.

Internal Source Calibration Section 8.

Self Calibration Section 4.

### 1.2 Internal Access

The high accuracy of the instrument demands that its internal environment remains undisturbed. The manufacturer's calibration certificate is invalidated if either of the covers is removed; this implies that at least a full External Calibration with Internal Source Characterization must follow any internal access, such as battery-changing, fault-finding or replacement of PCBs. Refer to Section 4.

N.B. Any displayed **CORRECTIONS ON** message refers to **Selfcal** corrections, generated by the most-recent self-calibration. If this was performed before the events mentioned in the above paragraph, then these corrections are not traceable to the new External Calibration and Internal Source Calibration. The message should be regarded as invalid until a **new Selfcal** is performed.

# 1.3 Remote Calibration via the IEEE 488 Interface

The 1281 is designed as a standards multimeter, its levels of accuracy demanding that it be calibrated against primary laboratory standards. The traceabilities of such standards are derived through physical devices which are as yet not remotely programmable, although the calibration facilities of the 1281 are included in its conformity to IEEE 488.2, against a time when such standards are available on the bus.

It is possible to characterize an individual calibration standard such as the Datron model 4708 at the levels required to calibrate a 1281 to its specification. The Datron 'Portocal' system can be programmed to perform these tasks automatically providing a 4708 in the system is adequately characterized. If the 1281 is not required to operate at its full specification, a regular 4708 in a remote system (e.g. Portocal) can easily be programmed to perform this task.

# 1.4 Special Calibration

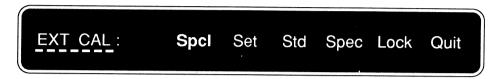

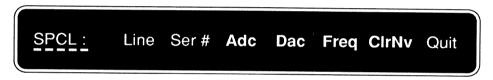

The main purpose of this section is to describe four Special Calibrations which may be required under certain conditions. These are listed on the SPCL menu, which is accessed via the EXT CAL menu when in CAL mode. They are:

Adc Calibration of the instrument's main multi-slope analog-to digital converter. *Refer to paras* 1.4.2.

Calibration of the digital-to-analog converter used for the optional 'Analog Output' of the instrument. *Refer to paras 1.4.3.*

Freq Calibrating the frequency detector responsible for the frequency readout in the SIGNAL FREQUENCY menu, which is accessed via the Monitor hard key then the Freq key in the MONITOR menu. The detector also provides the frequency readout used during SPOT CAL calibration. Refer to paras 1.4.4.

ClrNv Clearing a section of the non-volatile RAM. *Refer to paras 1.4.5.*

### **Special Calibration following Memory Corruption**

(e.g. When the battery which supplies the non-volatile calibration memory has been changed with the power off - see Section 4)

Section 2 (Fault Diagnosis) describes the device-dependent error codes resulting from internal tests. Error codes which are generated for calibration memory faults are listed on page 2-15.

Some of these refer to individual calibration correction errors, and others to combined errors.

When faced with any of these error codes, please seek advice or assistance from your nearest Datron Service Center.

When it is deemed necessary to carry out special calibration as a result of non-volatile memory corruption, the starting point should be to clear the calibration memory before proceeding with other individual calibrations.

Selecting CIrNv in the SPCL menu transfers to the CLEAR NV RAM menu which offers a choice of clearing one or all of three sections of RAM. The selection should be chosen as a result of consultation with technical staff at the service center.

# **Special Calibration Procedures**

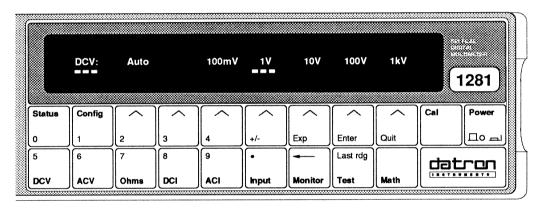

# 1.4.1 Entry into the SPCL Menu

To carry out anyof the four special calibrations it is first necessary to enter the SPCL menu via the EXT CAL menu. The EXT CAL menu is protected, and once active, the Caltrig key is enabled. For these reasons, users are referred to the 'Preparation' procedure detailed on page 8-7 of the User's handbook. Further details of the calibration facilities are described in Section 4 of the User's Handbook, beginning on page 4-40; the EXT CAL menu description starts on page 4-49.

### The EXT CAL Menu

Once the EXT CAL menu is active, pressing the SpcI soft key transfers to the SPCL menu.

## The SPCL Menu

The selection for setting the instrument to the local (50Hz or 60Hz) line frequency, and access for setting the instrument's serial number are also on this menu. We are not concerned with these here; details can be found in the User's Handbook Section 4 page 4-51. The four special calibrations highlighted in the above menu diagram are described in the following sub-sections 1.4.2 to 1.4.5.

## 1.4.2 Adc Key

To calibrate the main multi-slope analog-to digital converter.

The soft Adc key calibrates the different resolutions available from the main A-D converter, so that there are no significant differences in readings seen when changing resolutions with a constant input value.

This calibration is provided for use at manufacture and should need no further adjustment during the life of the instrument. However, if the calibration stores have been cleared or corrupted for any reason (for instance if the battery has been changed with the power off); or if a significant difference is found to exist between measurements of a constant input taken at different resolutions; then Adc calibration may be necessary.

### 1.4.2.1 To Calibrate:

No equipment is required, and the instrument does not need to be in any particular function or range.

Once in the SPCL menu, merely press the Adc soft key.

## 1.4.2.2 A-D Modes and Resolution

|         | Fast-on | Fast-off |

|---------|---------|----------|

| resin4+ | С       | D        |

| resin5+ | С       | D        |

| resin6+ | D       | F        |

| resin7+ | G       | G        |

| resin8+ | G       | G        |

## 1.4.2.3 A-D Modes and Power Line Cycles

| A-D Mode | Power Line<br>Cycles |

|----------|----------------------|

| C<br>D   | 3.33ms<br>1          |

| E        | 4                    |

| F        | 16                   |

| G        | 64                   |

## 1.4.2.3 List of Error Code Numbers

If the A-D calibration is not successful, one of the codes in the following table may be presented on the Menu display. If so, it is possible to rerun the individual test associated with the Error Code. Refer to Section 2, page 2-13 for access to the test pathways. As this is a complex A-D, it is stongly recommended that any problems should be referred to your nearest service center.

| Error<br>Code<br>No. | Test<br>Pathway<br>No. | Power<br>Line<br>Freq<br>(Hz) | A-D Mode<br>(Power Line<br>Cycles) | <b>Rdgs</b><br>(Discd)<br><b>A</b> vgd | Test<br>Type                  | Measured<br>Function     | Test Limits                                               |

|----------------------|------------------------|-------------------------------|------------------------------------|----------------------------------------|-------------------------------|--------------------------|-----------------------------------------------------------|

| 2030                 | PXXZ                   | 50                            | G (64)                             | 8 (0)                                  | Zero Noise                    | Std. Devn.               | < 0.2ppm                                                  |

| 2031                 | PXXY                   | 50                            | F (16)                             | (0) 8                                  | Zero Noise                    | Std. Devn.               | < 0.4ppm                                                  |

| 2032                 | PXXY                   | 50                            | F (16)                             | (0) 8                                  | Ext. Zero Noise               | Std. Devn.               | -200ppmR < 50Hz 16plc Zero < +200ppmR                     |

| 2033                 | PXXV                   | 50                            | E (4)                              | (0) 8                                  | Zero Noise                    | Std. Devn.               | < 1ppm                                                    |

| 2034                 | PXXV                   | 50                            | E (4)                              | (0) 8                                  | Ext. Zero Noise               | Std. Devn.<br>Std. Devn. | -200ppmR < 50Hz 4plc Zero < +200ppmR                      |

| 2035                 | PXXX<br>PXXX           | 50<br>50                      | D (1)                              | (0) 8<br>(0) 8                         | Zero Noise<br>Ext. Zero Noise | Std. Devn.               | < 2ppm<br>-200ppmR < 50Hz 1plc Zero < +200ppmR            |

| 2036<br>2037         | PXXW                   | 50                            | D (1)<br>C (3.33ms)                | (0) 8                                  | Zero Noise                    | Std. Devn.               | < 10ppm                                                   |

| 2038                 | PXXW                   | 50                            | C (3.33ms)                         | (0) 8                                  | Ext. Zero Noise               | Std. Devn.               | -200ppmR < 50Hz 3.33ms Zero < +200ppmR                    |

| 2040                 | PXXZ                   | 60                            | G (64)                             | (0) 8                                  | Zero Noise                    | Std. Devn.               | < 0.2ppm                                                  |

| 2041                 | PXXZ                   | 60                            | G (64)                             | (0) 8                                  | Ext. Zero Noise               | Std. Devn.               | -200ppmR < 60Hz 64plc Zero < +200ppmR                     |

| 2042                 | PXXY                   | 60                            | F (16)                             | (0) 8                                  | Zero Noise                    | Std. Devn.               | < 0.4ppm                                                  |

| 2043                 | PXXY                   | 60                            | F (16)                             | (0) 8                                  | Ext. Zero Noise               | Std. Devn.               | -200ppmR < 60Hz 16plc Zero < +200ppmR                     |

| 2044                 | PXXV<br>PXXV           | 60<br>60                      | E (4)                              | (0) 8<br>(0) 8                         | Zero Noise<br>Ext. Zero Noise | Std. Devn.<br>Std. Devn. | < 1ppm<br>-200ppmR < 60Hz 4plc Zero < +200ppmR            |

| 2045<br>2046         | PXXX                   | 60                            | E (4)<br>D (1)                     | (0) 8                                  | Zero Noise                    | Std. Devn.               | < 2ppm                                                    |

| 2047                 | PXXX                   | 60                            | D (1)                              | (0) 8                                  | Ext. Zero Noise               | Std. Devn.               | -200ppmR < 60Hz 1plc Zero < +200ppmR                      |

| 2048                 | PXXW                   | 60                            | C (3.33ms)                         | (0) 8                                  | Zero Noise                    | Std. Devn.               | < 10ppm                                                   |

| 2049                 | PXXW                   | 60                            | C (3.33ms)                         | (0) 8                                  | Ext. Zero Noise               | Std. Devn.               | -200ppmR < 60Hz 3.33ms Zero < +200ppmR                    |

| 2050                 | PXYZ                   | 50                            | G (64)                             | (8) 8                                  | +FR Noise                     | Std. Devn.               | < 0.2ppm                                                  |

| 2051                 | PXYY                   | 50                            | F (16)                             | (8) 8                                  | +FR Noise                     | Std. Devn.               | < 0.4ppm                                                  |

| 2052                 | PXYY                   | 50                            | F (16)                             | (8) 8                                  | +FR + Ext. Zero               | +FR gain                 | +FR - 100ppm < 50Hz 16plc +gain< +FR + 100ppm             |

| 2053                 | PXYV                   | 50                            | E (4)                              | (8) 8                                  | +FR Noise                     | Std. Devn.               | < 1ppm                                                    |

| 2054                 | PXYV<br>PXYX           | 50<br>50                      | E (4)<br>D (1)                     | (8) 8<br>(8) 8                         | +FR + Ext. Zero<br>+FR Noise  | +FR gain<br>Std. Devn.   | +FR - 100ppm < 50Hz 4plc +gain< +FR + 100ppm < 2ppm       |

| 2055<br>2056         | PXYX                   | 50                            | D (1)<br>D (1)                     | (8) 8                                  | +FR + Ext. Zero               | +FR gain                 | +FR - 100ppm < 50Hz 1plc +gain< +FR + 100ppm              |

| 2057                 | PXYW                   | 50                            | C (3.33ms)                         | (8) 8                                  | +FR Noise                     | Std. Devn.               | < 10ppm                                                   |

| 2058                 | PXYW                   | 50                            | C (3.33ms)                         | (8) 8                                  | +FR + Ext. Zero               | +FR gain                 | +FR - 100ppm < 50Hz 3.33ms +gain< +FR + 100ppm            |

| 2060                 | PXYZ                   | 60                            | G (64)                             | (8) 8                                  | +FR Noise                     | Std. Devn.               | < 0.2ppm                                                  |

| 2061                 | PXYZ                   | 60                            | F (16)                             | (8) 8                                  | +FR + Ext. Zero               | +FR gain                 | +FR - 100ppm < 60Hz 64plc +gain< +FR + 100ppm             |

| 2062                 | PXYY                   | 60<br>60                      | F (16)                             | (8) 8                                  | +FR Noise                     | Std. Devn.<br>+FR gain   | < 0.4ppm<br>+FR - 100ppm < 60Hz 16plc +gain< +FR + 100ppm |

| 2063<br>2064         | PXYY<br>PXYV           | 60<br>60                      | F (16)<br>E (4)                    | (8) 8<br>(8) 8                         | +FR + Ext. Zero<br>+FR Noise  | Std. Devn.               | < 1ppm                                                    |

| 2064                 | PXYV                   | 60                            | E (4)                              | (8) 8                                  | +FR + Ext. Zero               | +FR gain                 | * +FR - 100ppm < 60Hz 4plc +gain< +FR + 100ppm            |

| 2066                 | PXYX                   | 60                            | D (1)                              | (8) 8                                  | +FR Noise                     | Std. Devn.               | < 2ppm                                                    |

| 2067                 | PXYX                   | 60                            | D (1)                              | (8) 8                                  | +FR + Ext. Zero               | +FR gain                 | +FR - 100ppm < 60Hz 1plc +gain< +FR + 100ppm              |

| 2068                 | PXYW                   | 60                            | C (3.33ms)                         | (8) 8                                  | +FR Noise                     | Std. Devn.               | < 10ppm                                                   |

| 2069                 | PXYW                   | 60                            | C (3.33ms)                         | (8) 8                                  | +FR + Ext. Zero               | +FR gain                 | +FR - 100ppm < 60Hz 3.33ms +gain< +FR + 100ppm            |

| 2070                 | PXZZ                   | 50                            | G (64)                             | (8) 8                                  | -FR Noise                     | Std. Devn.               | < 0.2ppm                                                  |

| 2071                 | PXZY                   | 50                            | F (16)                             | (8) 8                                  | -FR Noise                     | Std. Devn.               | < 0.4ppm                                                  |

| 2072                 | PXZY                   | 50                            | F (16)                             | (8) 8                                  | -FR + Ext. Zero               | -FR gain                 | -FR - 100ppm < 50Hz 16plc -gain< -FR + 100ppm             |

| 2073                 | PXZV                   | 50<br>50                      | E (4)                              | (8) 8                                  | -FR Noise                     | Std. Devn.               | < 1ppm                                                    |

| 2074                 | PXZV                   | 50<br>50                      | E (4)                              | (8) 8                                  | -FR + Ext. Zero               | -FR gain                 | -FR - 100ppm < 50Hz 4plc -gain< -FR + 100ppm              |

| 2075<br>2076         | PXZX<br>PXZX           | 50<br>50                      | D (1)<br>D (1)                     | (8) 8<br>(8) 8                         | -FR Noise<br>-FR + Ext. Zero  | Std. Devn.<br>-FR gain   | < 2ppm<br>-FR - 100ppm < 50Hz 1plc -gain< -FR + 100ppm    |

| 2076                 | PXZX                   | 50<br>50                      | C (3.33ms)                         | (8) 8                                  | -FR Noise                     | Std. Devn.               | < 10ppm                                                   |

| 2078                 | PXZW                   | 50                            | C (3.33ms)                         | (8) 8                                  | -FR + Ext. Zero               | -FR gain                 | -FR - 100ppm < 50Hz 3.33ms -gain< -FR + 100ppm            |

| 2080                 | PXZZ                   | 60                            | G (64)                             | (8) 8                                  | -FR Noise                     | Std. Devn.               | < 0.2ppm                                                  |

| 2081                 | PXZZ                   | 60                            | F (16)                             | (8) 8                                  | -FR + Ext. Zero               | -FR gain                 | -FR - 100ppm < 60Hz 64plc -gain< -FR + 100ppm             |

| 2082                 | PXZY                   | 60                            | F (16)                             | (8) 8                                  | -FR Noise                     | Std. Devn.               | < 0.4ppm                                                  |

| 2083                 | PXZY                   | 60<br>60                      | F (16)                             | (8) 8                                  | -FR + Ext. Zero               | -FR gain                 | -FR - 100ppm < 60Hz 16plc -gain< -FR + 100ppm             |

| 2084<br>2085         | PXZV<br>PXZV           | 60<br>60                      | E (4)<br>E (4)                     | (8) 8<br>(8) 8                         | -FR Noise<br>-FR + Ext. Zero  | Std. Devn.<br>-FR gain   | < 1ppm<br>-FR - 100ppm < 60Hz 4plc -gain< -FR + 100ppm    |

| 2085                 | PXZV                   | 60<br>60                      | E (4)<br>D (1)                     | (8) 8                                  | -FR Noise                     | Std. Devn.               | < 2ppm                                                    |

|                      |                        |                               |                                    | (8) 8                                  | -FR + Ext. Zero               | -FR gain                 | -FR - 100ppm < 60Hz 1plc -gain< -FR + 100ppm              |

| 2087                 | PXZX                   | 60                            | D (1)                              | (0) 0                                  | 1 11 T LAL 2010               | -i ii gani               | Tit Tooppiil Cooliz this game Tit Tooppiil                |

# **Special Calibration Procedures (Contd.)**

## 1.4.3 Dac Key

To calibrate the digital-to-analog converter used for the optional 'Analog Output' of the instrument.

## **Analog Output Calibration**

The Analog Output (Option 70) can be provided to give an output scaled from any Function/Range combination to 1V Full Range at low impedance, whose purpose is to drive a logging chart or other recording device.

The Analog Output is calibrated at manufacture, and its accuracy is limited to 0.5% by the resolution of the Digital-to-Analog converter which produces the signal. The stability is such that further calibration of the D-A should be unnecessary during the life of the instrument. However, if the calibration stores have been cleared or corrupted for any reason (for instance if the battery has been changed with the power off); or if an analog output error is suspected to be greater than the specification; then Dac calibration may be required.

#### **Calibration Method**

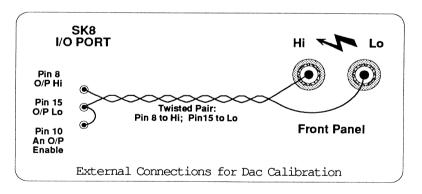

Calibration consists of stimulating the D-A from an internal digital source (representing nominal outputs), feeding the analog outputs from the I/O port back to the front panel Hi and Lo terminals (so that an output is known to exist at the I/O port pins) and using the (previously calibrated) 1V DC range to take accurate measurements. The values of these measurements determine digital corrections which are held in non-volatile memory.

No equipment is required other than the external connections shown in the diagram.

Once the external signal path has been connected; the analog output has been enabled; and the 1V DC range has been selected; the calibration can be performed automatically by pressing the **Dac** soft key.

### To Calibrate:

Ensure that the 1V DC range has already been calibrated.

Connect the Analog Output to the Front Panel Hi and Lo terminals as shown in the diagram. The connection between pins 10 and 15 of SK8 enables the Analog Output.

Select the 1V DC range and enter the SPCL menu via the EXT CAL menu.

Once in the SPCL menu, merely press the Dac soft key.

# **Special Calibration Procedures (Contd.)**

## 1.4.4 Freq

To calibrate the frequency detector responsible for the frequency readout in both SIGNAL FREQUENCY and SPOT CAL menus.

### **Frequency Readout Calibration**

The frequency of an incoming AC signal can be read out by pressing the Freq soft key when in the MONITOR menu. The SIGNAL FREQUENCY menu appears, with a live frequency reading which changes as the input frequency changes. An indication of the spot number of any calibrated spot frequency is also given. Refer to the User's Handbook starting at page 4-23.

In the STATUS CONFIG menu, access is given to review the spot frequencies at which the instrument has been calibrated; by selecting SpotF. Accurate calibration of the RMS gain, at each of the six spot frequencies which can be allocated to each ACV range, can be carried out when the instrument is in ACV Spot Frequency mode. Entry to the SPOT CAL menu is by selection of Set in the EXT CAL menu.

The frequency detector responsible for the frequency readout in all the above cases is calibrated at manufacture. The frequency stability of the detector is such that further calibration should be unnecessary during the life of the instrument. However, if the calibration stores have been cleared or corrupted for any reason (for instance if the battery has been changed with the power off); or if a frequency error is suspected; then **Freq** calibration may be required.

#### Calibration Method

Calibration consists of taking a measurement of an accurate 1MHz signal on the 1V AC range, and informing the computing system that the frequency is an accurate 1MHz. The measured frequency value contains the measurement error, which is used to determine a digital correction. This is held in non-volatile memory and applied for subsequent frequency readouts.

An accurate 1 MHz source is required to provide an external stimulus at between 0.6 V and 5.0 V peak-to-peak

Example Datron Model 4708

Once the external signal is injected; the 1V AC range has been selected; the calibration can be performed automatically by entering the SPCL menu via the EXT CAL menu and pressing the Freq soft key.

#### To Calibrate:

Select the 1V AC range and enter the SPCL menu via the EXT CAL menu.

Connect an accurate source of 1MHz at between 0.6V and 5.0V peak-to-peak to the Front Panel Hi and Lo terminals.

Press the Freq soft key.

# **Special Calibration Procedures (Contd.)**

### 1.4.5 CIrNv

To clear a section of the non-volatile RAM used for calibration memory.

### Caution:

Do not clear any section of RAM unless you are sure that it is absolutely necessary. You could destroy an expensive calibration!

## The CLEAR NV RAM Menu

Selecting **CIrNv** in the **SPCL** menu transfers to the **CLEAR NV RAM** menu which offers a choice of clearing one or all of three sections of RAM. The selection should be chosen only as a result of consultation with technical staff at your nearest service center.

### **Menu Choices**

| All  | Returns all the non-volatile RAM calibration memories to nominal values determined by firmware.                          |

|------|--------------------------------------------------------------------------------------------------------------------------|

| Ext  | Returns the external calibration and internal source characterization memories to nominal values determined by firmware. |

| Self | Returns the self calibration memories to nominal values determined by firmware.                                          |

| Hf   | Returns the calibration memories which hold the AC HF corrections to nominal values determined by firmware.              |

| Quit | Transfers back to the SPCL menu.                                                                                         |

# SECTION 2 GUIDE TO 1281 FAULT DIAGNOSIS

# 2.1 Introduction

### 2.1.1 Use of Error Codes

The 1281 incorporates an extensive set of error messages, each of which includes a code number. These messages can summarize incorrect application programming via the IEEE 488 bus, or a fault within the

instrument. They are intended to give the user a first indication that all is not well with the measurement which has been set up, and point the way to possible corrective action.

## 2.1.2 Code Groupings

The instrument is programmed in firmware to monitor its own operation, including interface protocols used via the IEEE 488 bus. As a result it will generate certain error codes to indicate that routine operations (including remote operation and some aspects of external calibration) are unsuccessful. Other error codes can be generated only from internal tests which are part of particular facilities initiated by the user, such as Selftest or Selfcal.

Because the remote operation of the instrument is designed to conform to the IEEE 488.2 standard, the large-scale categories of errors decreed by the standard have been used as the general basis for all error-reporting. This means that error codes and messages reported on the front panel display are consistent, as far as possible, with those reported via the IEEE 488 bus.

The type-names given to groupings of errors are thus primarily determined by those described in the IEEE 488.2 Standard specifications. Some categories apply only to bus operation, and are covered in Section 5 of the User's Handbook. Those which can be useful for diagnosing faults within the instrument are described in this section.

### Non-Recoverable Errors

For all Fatal System Errors, the error condition is reported only via the front panel (this may fail if the fault is severe enough and unfortunately located). The processor stops after displaying the message. A user must respond by first recording any Error Code and accompanying message displayed on the front panel. It is then permissible to power off and restart operation from power on. If this does not clear the error condition, repair should be initiated by communicating with the nearest Datron Service Center.

#### **Recoverable Errors**

These consist of Command Errors, Execution Errors and Device-Dependent Errors. The reported Execution and Device-Dependent Errors are each identified by a code number, placed in two separate Last-in/First-out queues.

The codes are displayed on the instrument front panel when in local control, or can be accessed at the controller when operating in remote control via the IEEE 488 bus. Many of the messages can be reported by both methods. The code number displayed on the instrument front panel is also accompanied by an error message.

'Command' and 'Execution' errors occur mainly because of incompatible remote programming via the IEEE 488 bus. 'Execution' and 'Device-Dependent' codes can result from specific errors during External Calibration, Self Calibration, Internal Reference parameter characterization or Input Zero operations. Some messages originate whenever a particular type of fault occurs. In addition to these automatic generations, self-testing can obtain a report about deviations from specified performance. Thus whenever it is suspected that a measurement (or a series of measurements) has not been completed successfully, a self test should be run which will either confirm the instrument's performance or localize any problem via the code number system.

# 2.1 Introduction (Contd.)

## 2.1.3 'Full' and 'Fast' Selftest

The front-panel test facilities are summarized in Section 4 of the User's Handbook (*page 4-30*). Two forms of self-test are available in the TEST menu, obtained by pressing the Test hard key:

#### **Full Selftest**

This measures the accuracy of all main instrument functions (DCV, ACV, DCI, ACI and Ohms) and ranges of those functions, after checking the internal references and A-D operation. 'PASS' or 'FAIL' results depend on the measurements falling within tolerance limits which reflect the instrument's specification. The accuracy of these tests depends on an initial comparison between the output voltages from the two internal reference modules, and then comparing the ratio of the two against the same ratio which existed at the 'Internal Source Characterization' carried out after the most-recent external calibration to obtain a 'Drift' figure.

### **Fast Selftest**

This is a subset of the set of tests allocated to a Full Selftest. It is intended as a quick 'Confidence' check to show that no serious defect is present to affect the instrument's operation. To increase the speed, only the most significant measurements from the full test are included, and most checks are run at reduced resolution (but the comparison between the reference ratio drift measurement is performed at full resolution).

The error code descriptions for Full Selftest are given in sub-section 2.6, and those codes used for Fast Selftest are repeated in sub-section 2.7 for easier access.

### 2.1.4 References in this Section

The messages are interpreted in this section to assist in fault localization:

| Fatal System Errors:                      | 2.2 |

|-------------------------------------------|-----|

| Command Errors:                           | 2.3 |

| Execution Errors:                         | 2.4 |

| Device-Dependent Errors - Index:          | 2.5 |

| Device-Dependent Errors - Full Test List: | 2.6 |

| Device-Dependent Errors - Fast Test List: | 2.7 |

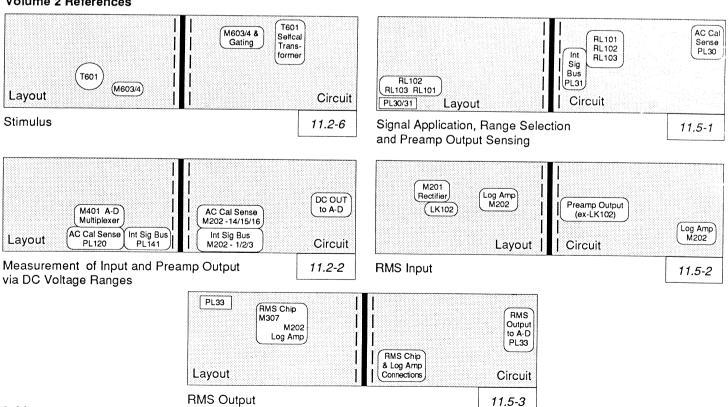

A grouped index of Device-Dependent error codes is given in sub-section 2.5. Each code carries a further reference to specific paragraphs and pages of sub-sections 2.6 and 2.7, in which the relevant element of the self-test responsible for generating the code number is described. Further references to the layout and circuit diagrams of Section 11 in Volume 2 also appear in sub-sections 2.6 and 2.7.

# 2.2 9000 Series Codes - Fatal System Errors

### 2.2.1 Introduction

System errors which cannot be recovered cause the system to halt with a message displayed (the processor stops after displaying the message). The error condition is reported only via the front panel, but this may fail if the fault is severe enough and unfortunately located.

### 2.2.2 Immediate Action

- Record any Error Code and accompanying message displayed on the front panel. Also record the hardware environment and any operations in progress at the time of failure. Fatal System errors are generally caused by hardware or software faults.

- 2. Power OFF and ON again to try to restart operation.

- 3. If (2) is unsuccessful, power OFF again and allow the instrument to cool for 15 minutes; then try powering ON.

- 4. If the error condition does not recur, repeat the original operations. Check that no temperature or configuration factors cause the error condition to return. If successful, carefully proceed with further measurements as required.

- 5. If (2) or (3) do not clear the error condition, or if it recurs in (4); communicate with your nearest Datron Service Center, quoting the recorded data from (1), and any other details. A form of failure report is given on the sheet inside the rear cover of this handbook.

# 2.2.3 Fatal System Error Codes

| Oouc | Type of Fault              |

|------|----------------------------|

|      |                            |

| 9000 | System Kernel Fault        |

| 9001 | Run Time System Error      |

| 9002 | Unexpected Exception       |

| 9003 | PROM Sumcheck Failure      |

| 9004 | RAM Check Failure          |

| 9005 | Serial Interface Fault     |

| 9006 | Option Test Failure        |

| 9007 | Unknown Engine Instruction |

| 9099 | Undefined Fatal Error      |

|      |                            |

Type of Fault

Code

## 2.3 Command Errors

Command Errors are reported in remote operation over the IEEE 488 bus. They are generated when the command has been 'parsed', but does not conform, either to the device command syntax, or to the IEEE 488.2 generic syntax.

The CME bit (5) is set true in the Standard-defined Event Status Byte, but there is no associated queue so no index can be given. The error is reported by the mechanisms described in the sub-section dealing with status reporting, in Section 5 of the User's Handbook.

## 2.4 1000 Series Codes - Execution Errors

### 2.4.1 Introduction

An Execution Error is generated if a command is recognised as valid (ie can be parsed and does not generate a Command Error), but cannot be executed because it is incompatible with the current device state, or because it attempts to command parameters which are out-of-limits.

### **Local Operation**

Most normal operations, from the front panel, lock out the conditions which would give rise to Excecution errors, by the choices not being offered in the appropriate menus. However, some selections can be made using hard keys (such as pressing ACV when the option is not present in the instrument) which cannot be locked out. In these cases the Execution error is used as an aide-memoire for the user's convenience. The error code number appears on the front-panel Menu display, accompanied by an error message.

### **Remote Operation**

The EXE bit (4) is set true in the Standard-defined Event Status Byte, and the error code number is appended to the Execution Error queue. The error is reported by the mechanisms described in the sub-section dealing with status reporting in Section 5 of the User's Handbook, and the queue entries can be read destructively as LIFO by the Common query command \*EXQ?.

### 2.4.2 Execution Error Codes

| Code | Type of Error                          |

|------|----------------------------------------|

| 1000 | EXE queue empty when recalled          |

| 1001 | Option not installed                   |

| 1002 | Calibration disabled                   |

| 1003 | Ratio/Function combination not allowed |

| 1004 | Filter incompatible with Function      |

| 1005 | Input Zero not allowed                 |

| 1006 | Calibration not allowed in Ratio       |

| 1007 | Data entry error                       |

| 1008 | Must be in AC Function                 |

| 1009 | Pass Number entry error                |

|      |                                        |

| 1010 | Divide-by-zero not allowed             |

| 1011 | Must be in SpotF Function              |

| 1012 | No more errors in the queue            |

| 1013 | Data out of limit                      |

| 1014 | Illegal Range/Function combination     |

| 1015 | Command allowed only in Remote         |

| 1016 | Not in Special Calibration             |

| 1017 | Calibration not allowed with Math      |

| 1018 | Key not in the Cal Enabled position    |

| 1019 | Spec not compatible with Function      |

|      |                                        |

| 1020 | Internal Source Cal required           |

| 1021 | Test not allowed when Cal enabled      |

| 1022 | No parameter for this Function         |

|      |                                        |

# 2.5 2000 Series Codes - Device-Dependent Errors - Index

### 2.5.1 Introduction

A Device-Dependent Error is generated if the device detects an internal operating fault (eg. during Selfcal or Selftest). The DDE bit (3) is set *true* in the Standard-defined Event Status Byte, and the error code number is appended to the Device-Dependent Error queue.

### Remote Operation

In Remote, the error is reported by the mechanisms described in the subsection dealing with status reporting in Section 5 of the User's Handbook, and the queue entries can be read destructively as LIFO by the query DDO?.

### **Local Operation**

In Local, the Device-Dependent Error queue is checked at the end of the operation (eg. Cal, Zero, Test). If *true*, an error has occurred, and the contents of the most-recent entry in the queue is displayed on the front panel. The act of displaying the message deletes its code from the queue, so the next most-recent code comes to the front of the queue and is available to be displayed. The queue must be empty for normal operation to continue.

If both bus and front panel users attempt to read the queue concurrently, the data is read out destructively on a first-come, first-served basis. Thus one of the users cannot read the data on one interface as it has already been destroyed by reading on the other. This difficulty should be solved by suitable application programming to avoid the possibility of a double readout. Ideally the IEEE 488 interface should set the instrument into REMS or RWLS to prevent confusion. The bus can ignore the queue, but the front panel user will have to read it to continue.

# 2.5.2 Index of Device-Dependent Error Codes

| Code Immediate Action                                                        | Full Test Ref<br>Sect.                                                                                     | Full Test Reference<br>Sect. Page                            |                                          | ference<br>Page              |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------|------------------------------|

| Memory Tests                                                                 |                                                                                                            |                                                              |                                          |                              |

| 2000<br>2001<br>2002<br>2003<br>2004<br>2008                                 | 2.6.4.1<br>2.6.4.1<br>2.6.4.1<br>2.6.4.1<br>2.6.4.1<br>2.6.4.1                                             | 2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15                 |                                          |                              |

| 2010<br>2011<br>2012<br>2013<br>2014<br>2015<br>2016<br>2017<br>2018<br>2019 | 2.6.4.1<br>2.6.4.1<br>2.6.4.2<br>2.6.4.2<br>2.6.4.2<br>2.6.4.2<br>2.6.4.2<br>2.6.4.2<br>2.6.4.2<br>2.6.4.2 | 2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15 |                                          |                              |

| 2100°<br>2101°<br>2102°<br>2103°                                             | 2.6.5.1<br>2.6.5.1<br>2.6.5.1<br>2.6.5.1                                                                   | 2-15<br>2-15<br>2-15<br>2-15                                 | 2.7.1.1<br>2.7.1.1<br>2.7.1.1<br>2.7.1.1 | 2-58<br>2-58<br>2-58<br>2-58 |

| Fuse Tests                                                                   |                                                                                                            |                                                              |                                          |                              |

| 2111*                                                                        | 2.6.5.2                                                                                                    | 2-1                                                          |                                          |                              |

| Others                                                                       |                                                                                                            |                                                              |                                          |                              |

| 2114<br>2115                                                                 | 2.6.5.3<br>2.6.5.3                                                                                         | 2-15<br>2-15                                                 |                                          |                              |

| Reference Ratio Tests                                                        |                                                                                                            |                                                              |                                          |                              |

| 2121*<br>2122*                                                               | 2.6.6.1<br>2.6.6.1                                                                                         | 2-16<br>2-16                                                 | 2.7.2<br>2.7.2                           | 2-58<br>2-58                 |

| 2131*<br>2132*                                                               | 2.6.6.2<br>2.6.6.2                                                                                         | 2-16<br>2-16                                                 | 2.7.2<br>2.7.2                           | 2-58<br>2-58                 |

| 2141*<br>2142*<br>2143                                                       | 2.6.6.3<br>2.6.6.3<br>2.6.6.3                                                                              | 2-16<br>2-16<br>2-16                                         | 2.7.2<br>2.7.2                           | 2-58<br>2-58                 |

| 2151* 2152* 2153* 2154* 2155 2156                                            | 2.6.6.4<br>2.6.6.4<br>2.6.6.4<br>2.6.6.4<br>2.6.6.4<br>2.6.6.4                                             | 2-16<br>2-16<br>2-16<br>2-16<br>2-16<br>2-16                 | 2.7.2<br>2.7.2<br>2.7.2<br>2.7.2         | 2-58<br>2-58<br>2-58<br>2-58 |

| Section 2 - Fault Diagnosis |                    |              |                    |              |  |

|-----------------------------|--------------------|--------------|--------------------|--------------|--|

| Code Immediate Action       | Full Test F        |              |                    | Reference    |  |

|                             | Sect.              | Page         | Sect               | Page         |  |

| DC Voltage Tests            |                    |              |                    |              |  |

| 2161                        | 2.6.7.1            | 2-18         |                    |              |  |

| 2162<br>2163                | 2.6.7.1<br>2.6.7.1 | 2-18         |                    |              |  |

| 2171                        |                    | 2-18         |                    |              |  |

| 2172                        | 2.6.7.1<br>2.6.7.1 | 2-18<br>2-18 |                    |              |  |

| 2173                        | 2.6.7.1            | 2-18         |                    |              |  |

| 2181*                       | 2.6.7.1            | 2-18         | 2.7.3.1            | 2-60         |  |

| 2182*                       | 2.6.7.1            | 2-18         | 2.7.3.1            | 2-60         |  |

| 2183                        | 2.6.7.1            | 2-18         |                    |              |  |

| 2191<br>2192                | 2.6.7.1<br>2.6.7.1 | 2-18<br>2-18 |                    |              |  |

| 2193                        | 2.6.7.1            | 2-18         |                    |              |  |

| 2201                        | 2.6.7.1            | 2-18         |                    |              |  |

| 2202                        | 2.6.7.1            | 2-18         |                    |              |  |

| 2203                        | 2.6.7.1            | 2-18         |                    |              |  |

| 2211*<br>2212*              | 2.6.7.2<br>2.6.7.2 | 2-20<br>2-20 | 2.7.3.2<br>2.7.3.2 | 2-60         |  |

| 2213*                       | 2.6.7.2            | 2-20         | 2.7.3.2            | 2-60<br>2-60 |  |

| 2214*                       | 2.6.7.2            | 2-20         | 2.7.3.2            | 2-60         |  |

| 2215*<br>2216*              | 2.6.7.2<br>2.6.7.2 | 2-20<br>2-20 | 2.7.3.2<br>2.7.3.2 | 2-60<br>2-60 |  |

| 2221                        | 2.6.7.3            | 2-22         | 2.7.0.2            | 2 00         |  |

| 2222                        | 2.6.7.2            | 2-22         |                    |              |  |

| 2223<br>2224                | 2.6.7.2            | 2-22         |                    |              |  |

| 2231                        | 2.6.7.2            | 2-22         |                    |              |  |

| 2232                        | 2.6.7.2<br>2.6.7.2 | 2-22<br>2-22 |                    |              |  |

| 2233                        | 2.6.7.2            | 2-22         |                    |              |  |

| 2234                        | 2.6.7.2            | 2-22         |                    |              |  |

| 2241<br>2242                | 2.6.7.2            | 2-22         |                    |              |  |

| 2243                        | 2.6.7.2<br>2.6.7.2 | 2-22<br>2-22 |                    |              |  |

| 2251                        | 2.6.7.2            | 2-22         |                    |              |  |

| 2252                        | 2.6.7.2            | 2-22         |                    |              |  |

| 2253                        | 2.6.7.2            | 2-22         |                    |              |  |

| 2261<br>2262                | 2.6.7.2            | 2-22         |                    |              |  |

| 2263                        | 2.6.7.2<br>2.6.7.2 | 2-22<br>2-22 |                    |              |  |

| 2271                        | 2.6.7.2            | 2-24         |                    |              |  |

| 2272                        | 2.6.7.2            | 2-24         |                    |              |  |

| 2273                        | 2.6.7.2            | 2-24         |                    |              |  |

| 2281*<br>2282*              | 2.6.7.2            | 2-24         | 2.7.3.3            | 2-60         |  |

| 2283                        | 2.6.7.2<br>2.6.7.2 | 2-24<br>2-24 | 2.7.3.3            | 2-60         |  |

| 2291                        | 2.6.7.2            | 2-24         |                    |              |  |

| 2292                        | 2.6.7.2            | 2-24         |                    |              |  |

| 2293                        | 2.6.7.2            | 2-24         |                    |              |  |

|                                                                |                  | Section 2 - Fault Diagno                                                             |                                                              |                    |                                  | uit Diagnosis |  |  |

|----------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|----------------------------------|---------------|--|--|

| Code                                                           | Immediate Action | Full Test Re<br>Sect.                                                                | Full Test Reference<br>Sect. Page                            |                    | Fast Test Reference<br>Sect Page |               |  |  |

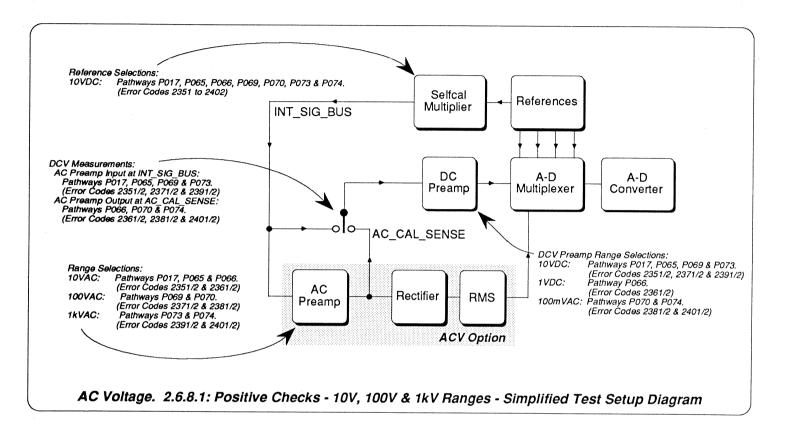

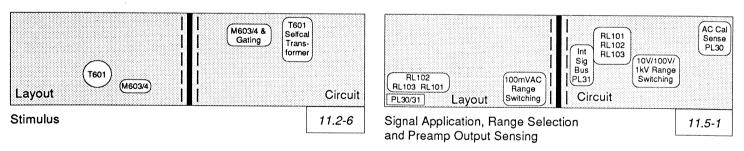

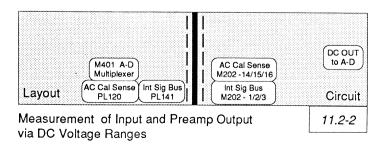

| AC Vo                                                          | oltage Tests     |                                                                                      | 3                                                            |                    | J                                |               |  |  |

| 2301<br>2302                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-26<br>2-26                                                 |                    |                                  |               |  |  |

| 2311*<br>2312*                                                 |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-26<br>2-26                                                 | 2.7.4.1<br>2.7.4.1 | 2-62<br>2-62                     |               |  |  |

| 2321*<br>2322*                                                 |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-26<br>2-26                                                 | 2.7.4.1<br>2.7.4.1 | 2-62<br>2-62                     |               |  |  |

| 2331<br>2332                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-26<br>2-26                                                 |                    |                                  |               |  |  |

| 2341*<br>2342*                                                 |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-26<br>2-26                                                 | 2.7.4.1<br>2.7.4.1 | 2-62<br>2-62                     |               |  |  |

| 2351<br>2352                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-28<br>2-28                                                 |                    |                                  |               |  |  |

| 2361<br>2362                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-28<br>2-28                                                 |                    |                                  |               |  |  |

| 2371<br>2372                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-28<br>2-28                                                 |                    |                                  |               |  |  |

| 2381<br>2382                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-28<br>2-28                                                 |                    |                                  |               |  |  |

| 2391<br>2392                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-28<br>2-28                                                 |                    |                                  |               |  |  |

| 2401<br>2402                                                   |                  | 2.6.8.1<br>2.6.8.1                                                                   | 2-28<br>2-28                                                 |                    |                                  |               |  |  |

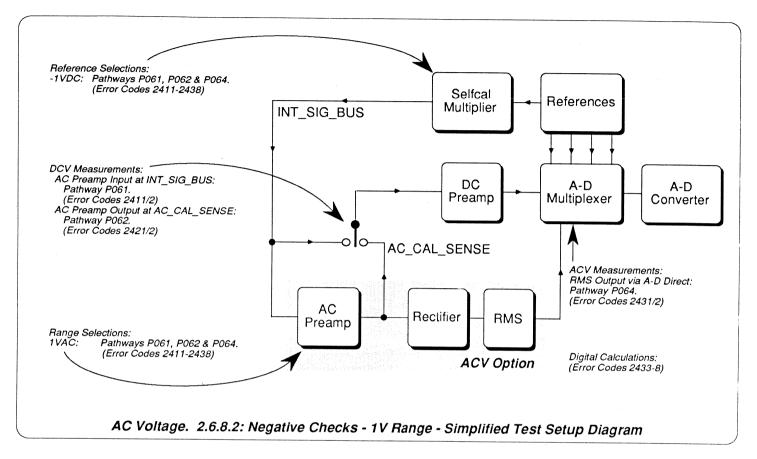

| 2411<br>2412                                                   |                  | 2.6.8.2<br>2.6.8.2                                                                   | 2-30<br>2-30                                                 |                    |                                  |               |  |  |

| 2421*<br>2422*                                                 |                  | 2.6.8.2<br>2.6.8.2                                                                   | 2-30<br>2-30                                                 | 2.7.4.2<br>2.7.4.2 | 2-64<br>2-64                     |               |  |  |

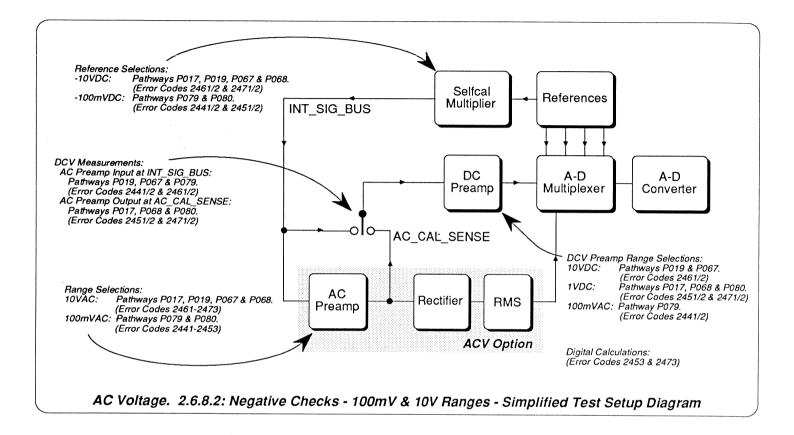

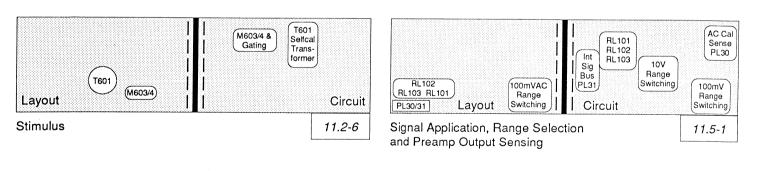

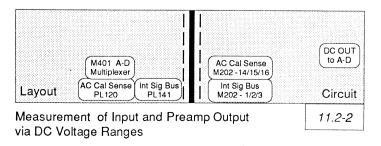

| 2431*<br>2432*<br>2433<br>2434<br>2435<br>2436<br>2437<br>2438 |                  | 2.6.8.2<br>2.6.8.2<br>2.6.8.2<br>2.6.8.2<br>2.6.8.2<br>2.6.8.2<br>2.6.8.2<br>2.6.8.2 | 2-30<br>2-30<br>2-30<br>2-30<br>2-30<br>2-30<br>2-30<br>2-30 | 2.7.4.2<br>2.7.4.2 | 2-64<br>2-64                     |               |  |  |

| 2441<br>2442                                                   |                  | 2.6.8.2<br>2.6.8.2                                                                   | 2-32<br>2-32                                                 |                    |                                  |               |  |  |

| 2451<br>2452<br>2453                                           |                  | 2.6.8.2<br>2.6.8.2<br>2.6.8.2                                                        | 2-32<br>2-32<br>2-32                                         |                    |                                  |               |  |  |

| 2461<br>2462                                                   |                  | 2.6.8.2<br>2.6.8.2                                                                   | 2-32<br>2-32                                                 |                    |                                  |               |  |  |

| 2471*<br>2472*<br>2473                                         |                  | 2.6.8.2<br>2.6.8.2<br>2.6.8.2                                                        | 2-32<br>2-32<br>2-32                                         | 2.7.4.2<br>2.7.4.2 | 2-64<br>2-64                     |               |  |  |

| 2481<br>2482                                                   |                  | 2.6.8.2<br>2.6.8.2                                                                   | 2-34<br>2-34                                                 |                    |                                  |               |  |  |

| 2491*<br>2492*<br>2493                                         |                  | 2.6.8.2<br>2.6.8.2<br>2.6.8.2                                                        | 2-34<br>2-34<br>2-34                                         | 2.7.4.2<br>2.7.4.2 | 2-64<br>2-64                     |               |  |  |

| 2501<br>2502                                                   |                  | 2.6.8.2<br>2.6.8.2                                                                   | 2-34<br>2-34                                                 |                    |                                  |               |  |  |

| 2511*<br>2512*<br>2513                                         |                  | 2.6.8.2<br>2.6.8.2<br>2.6.8.2                                                        | 2-34<br>2-34<br>2-34                                         | 2.7.4.2<br>2.7.4.2 | 2-64<br>2-64                     |               |  |  |

Section 2 - Fault Diagnosis

| ode Immediate Action | Full Test | Full Test Reference |       | Fast Test Reference |  |  |

|----------------------|-----------|---------------------|-------|---------------------|--|--|

|                      | Sect.     | Page                | Sect  | Page                |  |  |

| C Current Tests      |           |                     |       |                     |  |  |

| 21                   | 2.6.9     | 2-36                |       |                     |  |  |

| 22                   | 2.6.9     | 2-36                |       |                     |  |  |

| 23                   | 2.6.9     | 2-36                |       |                     |  |  |

| 24                   | 2.6.9     | 2-36                |       |                     |  |  |

| 25                   | 2.6.9     | 2-36                |       |                     |  |  |

| 31*                  | 2.6.9     | 2-36                | 2.7.5 | 2-66                |  |  |

| 32*                  | 2.6.9     | 2-36                | 2.7.5 | 2-66                |  |  |

| 33                   | 2.6.9     | 2-36                |       | 2 00                |  |  |

| 41                   | 2.6.9     | 2-38                |       |                     |  |  |

| 42                   | 2.6.9     | 2-38                |       |                     |  |  |

| 43                   | 2.6.9     | 2-38                |       |                     |  |  |

| 51*                  | 2.6.9     | 2-38                | 2.7.5 | 2-66                |  |  |

| 52*                  | 2.6.9     | 2-38                | 2.7.5 | 2-66                |  |  |

| 53                   | 2.6.9     | 2-38                |       |                     |  |  |

| 61                   | 2.6.9     | 2-38                |       |                     |  |  |

| 62                   | 2.6.9     | 2-38                |       |                     |  |  |

| 63                   | 2.6.9     | 2-38                |       |                     |  |  |

| 71*                  | 2.6.9     | 2-38                | 2.7.5 | 2-66                |  |  |

| 72*                  | 2.6.9     | 2-38                | 2.7.5 | 2-66                |  |  |

| 73                   | 2.6.9     | 2-38                |       |                     |  |  |

| 81                   | 2.6.9     | 2-40                |       |                     |  |  |

| 82                   | 2.6.9     | 2-40                |       |                     |  |  |

| 83                   | 2.6.9     | 2-40                |       |                     |  |  |

| 91*                  | 2.6.9     | 2-40                | 2.7.5 | 2-66                |  |  |

| 92*                  | 2.6.9     | 2-40                | 2.7.5 | 2-66                |  |  |

| 93                   | 2.6.9     | 2-40                |       |                     |  |  |

| 01                   | 2.6.9     | 2-40                |       |                     |  |  |

| 02                   | 2.6.9     | 2-40                |       |                     |  |  |

| 03                   | 2.6.9     | 2-40                |       |                     |  |  |

| 11*                  | 2.6.9     | 2-40                | 2.7.5 | 2-66                |  |  |

| 12*                  | 2.6.9     | 2-40                | 2.7.5 | 2-66                |  |  |

| 13                   | 2.6.9     | 2-40                |       |                     |  |  |

| Full Test R<br>Sect. | Reference<br>Page                                                                                                                                            | Fast Test<br>Sect                                                                                                                                                                                                                                                                                           | Reference<br>Page                                                                                                                                                                                                                                                                                                                                                       |        |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Sect.                | Page                                                                                                                                                         | Sect                                                                                                                                                                                                                                                                                                        | Page                                                                                                                                                                                                                                                                                                                                                                    |        |

|                      |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                       |        |

|                      |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                         |        |

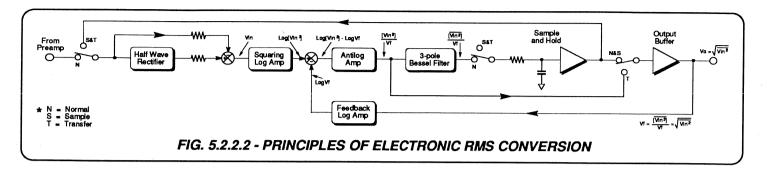

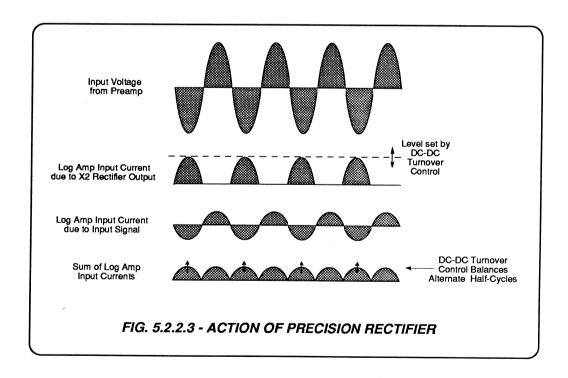

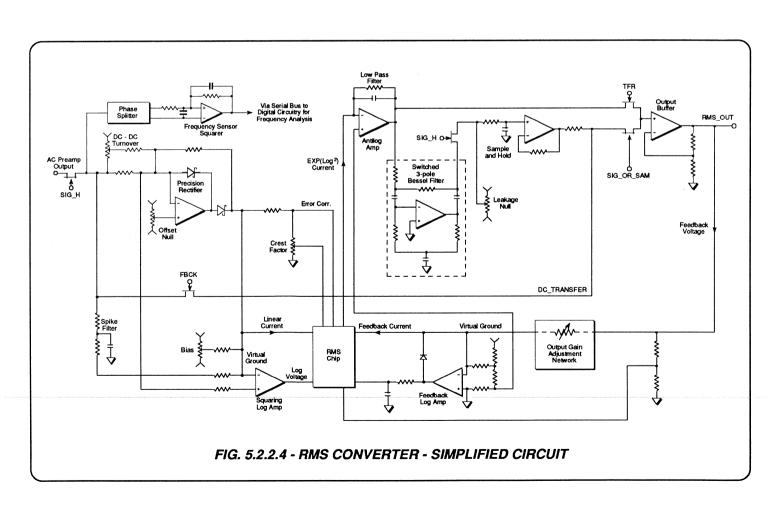

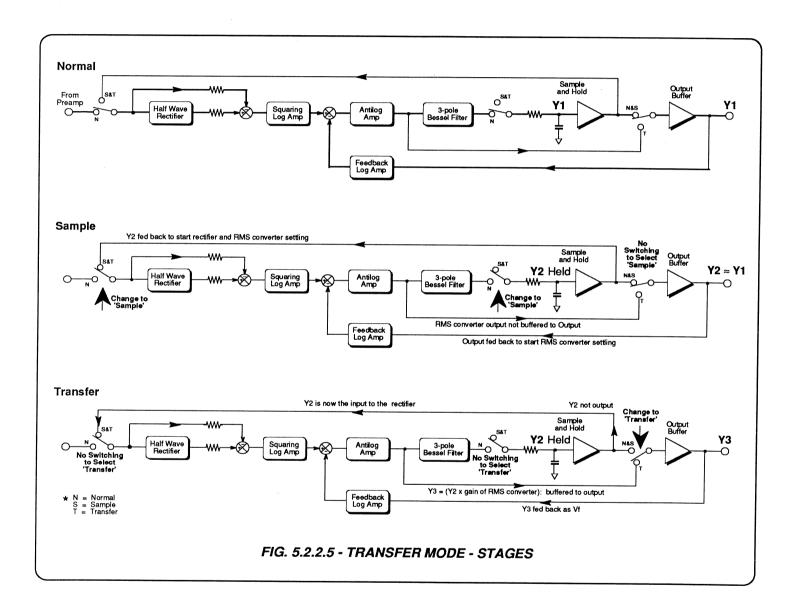

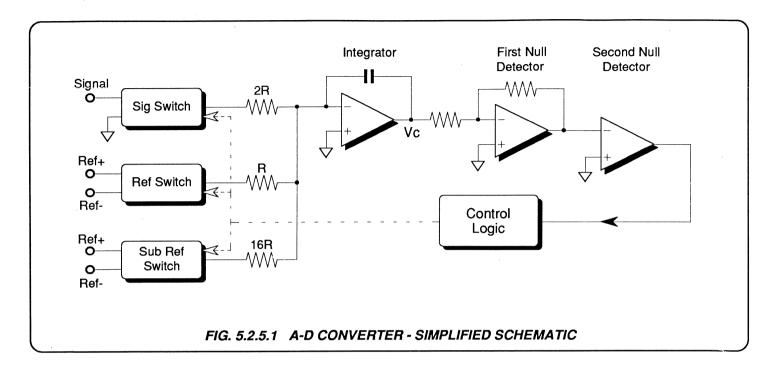

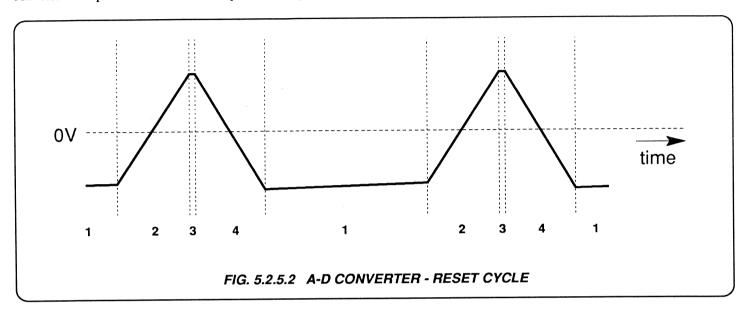

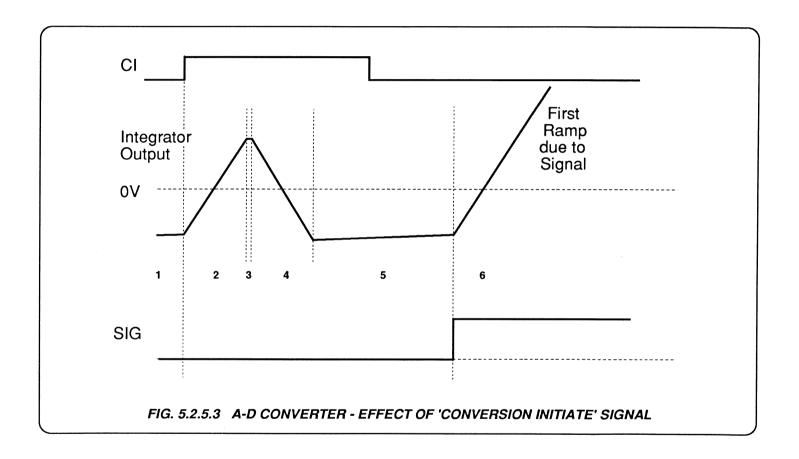

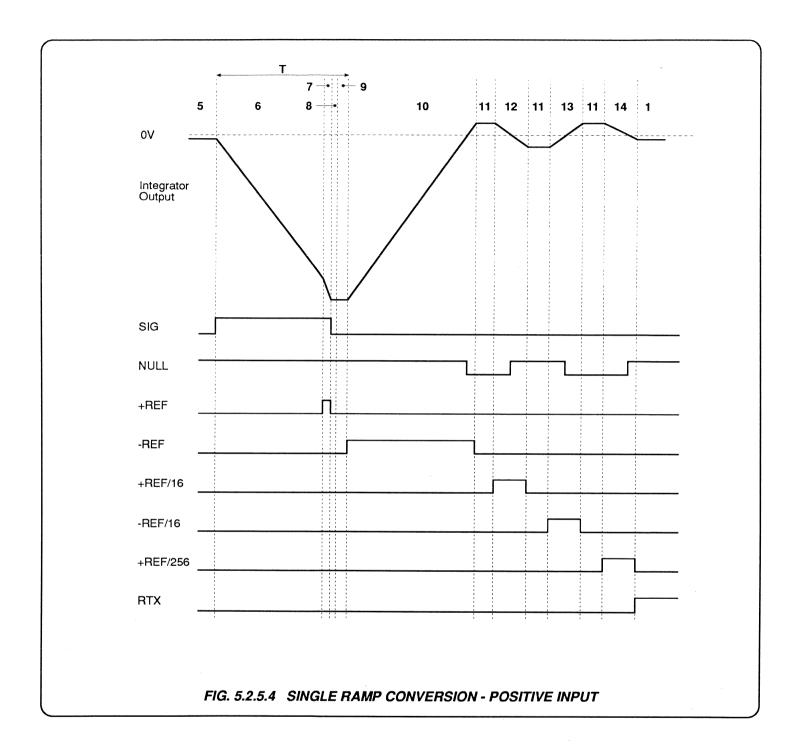

| 2.6.10               | 2-42                                                                                                                                                         |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                         |        |